## CYF1018V CYF1036V CYF1072V

## 18/36/72-Mbit Programmable 2-Queue FIFOs

#### Features

- Memory organization

- Industry's largest first in first out (FIFO) memory densities: 18-Mbit, 36-Mbit, 72-Mbit

- Selectable memory organization: × 9, × 12, × 16, × 18, × 20, × 24, × 32, × 36

- Up to 100-MHz clock operation

- Unidirectional operation

- Independent read and write ports

- Supports simultaneous read and write operations

- Reads and writes operate on independent clocks upto a maximum clock ratio of 2, enabling data buffering across clock domains

- Supports multiple I/O voltage standard: Low voltage complementary metal oxide semiconductor (LVCMOS) 3.3 V and 1.8 V voltage standards.

- Output enable control for read skip operations

- User configured two-Queue operating mode

- Mark and retransmit: resets read pointer to user marked position

- Empty and full status flags

- Flow-through mailbox register to send data from input to output port, bypassing the FIFO sequence

- Configure programmable flags and registers through serial or parallel modes

- Separate serial clock (SCLK) input for serial programming

- Master reset to clear entire FIFO

- Joint test action group (JTAG) port provided for boundary scan function

- Industrial temperature range: -40 °C to +85 °C

## **Functional Description**

The Cypress programmable FIFO family offers the industry's highest-density programmable FIFO memory device. It has independent read and write ports, which can be clocked up to 100 MHz. User can configure input and output bus sizes. The maximum bus size of 36 bits enables a maximum data throughput of 3.6 Gbps. The read and write ports can support multiple I/O voltage standards. The user-programmable registers enable user to configure the device operation as desired. The device also offers a simple and easy-to-use interface to reduce implementation and debugging efforts, improve time-to-market, and reduce engineering costs. This makes it an ideal memory choice for a wide range of applications including multiprocessor interfaces, video and image processing, networking and telecommunications, high-speed data acquisition, or any system that needs buffering at very high speeds across different domains.

As implied by the name, the functionality of the FIFO is such that the data is read out of the read port in the same sequence in which it was written into the write port. The data is sequentially written into the FIFO from the write port gets written into the device at the rising edge of the write clock. Enabling the reads and outputs fetches data on the read port at every rising edge of the read clock. Both reads and writes can occur simultaneously at different speeds provided the ratio of read to write clock is between 0.5 and 2. Appropriate flags are set whenever the FIFO is empty or full.

The device also supports two-Queue operation, mark and retransmit of data, and a flow-through mailbox register.

All product features and specs are common to all densities (CYF1072V, CYF1036V, and CYF1018V) unless otherwise specified. All descriptions are given assuming the device is CYF1072V operated in × 36 mode. They hold good for other densities (CYF1036V, and CYF1018V) and all port sizes × 9, ×12, × 16, × 18, × 20, × 24 and × 32 unless otherwise specified. the only difference will be in the input and output bus width.

Table 1 on page 8 shows the part of bus with valid data from D[35:0] and Q[35:0] in  $\times$  9,  $\times$  12,  $\times$  16,  $\times$  18,  $\times$  20,  $\times$  24,  $\times$  32 and  $\times$  36 modes.

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised September 28, 2011

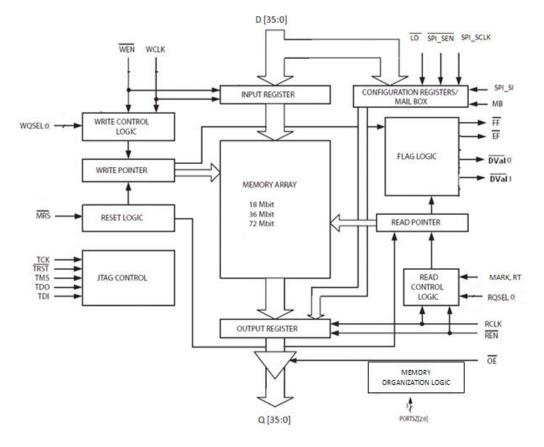

## Logic Block Diagram

## Contents

| Pin Diagram for CYF1XXXV                     | 4  |

|----------------------------------------------|----|

| Pin Definitions                              |    |

| Architecture                                 |    |

| Reset Logic                                  | 7  |

| Flag Operation                               |    |

| Full Flag                                    |    |

| Empty Flag                                   |    |

| Retransmit from Mark Operation               | 7  |

| Flow-through mailbox Register                | 7  |

| Selecting Word Sizes                         |    |

| Data Valid Signal                            | 8  |

| Power Up                                     | 8  |

| Read Skip Operation                          | 8  |

| Multi-Queue Operation                        | 8  |

| Width Expansion Configuration                | 10 |

| Memory Organization for Different Port Sizes | 11 |

| Read/Write Clock Requirements                | 11 |

| JTAG operation                               |    |

| Maximum Ratings                              | 13 |

| Operating Range                         |   |

|-----------------------------------------|---|

| Recommended DC Operating Conditions     |   |

| Electrical Characteristics              |   |

| I/O Characteristics                     | - |

| Latency Table                           |   |

| Switching Characteristics               |   |

| Switching Waveforms                     |   |

| Ordering Information                    |   |

| Ordering Code Definitions               |   |

| Package Diagram                         |   |

| Acronyms                                |   |

| Document Conventions                    |   |

| Units of Measure                        |   |

| Document History Page                   |   |

| Sales, Solutions, and Legal Information |   |

| Worldwide Sales and Design Support      |   |

| Products                                |   |

| PSoC Solutions                          |   |

|                                         |   |

## Pin Diagram for CYF1XXXV

|   | ······································ |       |      |        |         |                    |          |        |       |       |       |

|---|----------------------------------------|-------|------|--------|---------|--------------------|----------|--------|-------|-------|-------|

|   | 1                                      | 2     | 3    | 4      | 5       | 6                  | 7        | 8      | 9     | 10    | 11    |

| А | FF                                     | D0    | D1   | WQSEL0 | PORTSZ0 | PORTSZ1            | DNU      | RQSEL0 | RT    | Q0    | Q1    |

| В | EF                                     | D2    | D3   | DNU    | DNU     | PORTSZ2            | DNU      | DNU    | REN   | Q2    | Q3    |

| С | D4                                     | D5    | WEN  | DNU    | VCC1    | DNU                | VCC1     | DNU    | RCLK  | Q4    | Q5    |

| D | D6                                     | D7    | VSS  | VCC1   | DNU     | LD                 | DNU      | VCC1   | VSS   | Q6    | Q7    |

| Е | D8                                     | D9    | VCC2 | VCC2   | VCCIO   | VCCIO              | VCCIO    | VCC2   | VCC2  | Q8    | Q9    |

| F | D10                                    | D11   | VSS  | VSS    | VSS     | DNU                | VSS      | VSS    | VSS   | Q10   | Q11   |

| G | D12                                    | D13   | VCC2 | VCC2   | VCCIO   | VCC1               | VCCIO    | VCC2   | VCC2  | Q12   | Q13   |

| Н | D14                                    | D15   | VSS  | VSS    | VSS     | VCC1               | VSS      | VSS    | VSS   | Q14   | Q15   |

| J | D16                                    | D17   | VCC2 | VCC2   | VCCIO   | VCC1               | VCCIO    | VCC2   | VCC2  | Q16   | Q17   |

| к | DNU                                    | DNU   | WCLK | DNU    | VSS     | DNU                | VSS      | DNU    | VCCIO | VCCIO | VCCIO |

| L | D18                                    | D19   | VCC2 | VCC2   | VCCIO   | VCC1               | VCCIO    | VCC2   | VCC2  | Q18   | Q19   |

| М | D20                                    | D21   | VSS  | VSS    | VSS     | VCC1               | VSS      | VSS    | VSS   | Q20   | Q21   |

| Ν | D22                                    | D23   | VCC2 | VCC2   | VCCIO   | VCC1               | VCCIO    | VCC2   | VCC2  | Q22   | Q23   |

| Ρ | D24                                    | D25   | VSS  | VSS    | VSS     | SPI_SEN            | VSS      | VSS    | VSS   | Q24   | Q25   |

| R | D26                                    | D27   | VCC2 | VCC2   | VCCIO   | VCCIO              | VCCIO    | VCC2   | VCC2  | Q26   | Q27   |

| Т | D28                                    | D29   | VSS  | VCC1   | VCC1    | SPI_SI             | VCC1     | VCC1   | VSS   | Q28   | Q29   |

| U | DVal0                                  | DNU   | D30  | D31    | DNU     | DNU <sup>[1]</sup> | SPI_SCLK | Vref   | OE    | Q30   | Q31   |

| V | DNU                                    | DNU   | D32  | D33    | DNU     | MRS                | MB       | DNU    | MARK  | Q32   | Q33   |

| W | TDO                                    | DVal1 | D34  | D35    | TDI     | TRST               | TMS      | ТСК    | Vref  | Q34   | Q35   |

#### Figure 1. 209-ball FBGA (Top View)

## **Pin Definitions**

| Pin Name         | I/O             | Pin Description                                                                                                                                                                                                                                                                                             |  |  |  |

|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D[35:0]          | Input           | Data inputs: Data inputs for a 36-bit bus.                                                                                                                                                                                                                                                                  |  |  |  |

| Q[35:0]          | Output          | Data outputs: Data outputs for a 36-bit bus.                                                                                                                                                                                                                                                                |  |  |  |

| WEN              | Input           | Vrite enable: WEN enables WCLK to write data into the FIFO memory and configuration registers.                                                                                                                                                                                                              |  |  |  |

| REN              | Input           | Read enable: REN enables RCLK to read data from the FIFO memory and configuration registers.                                                                                                                                                                                                                |  |  |  |

| ŌĒ               | Input           | Output enable: When $\overline{OE}$ is LOW, FIFO data outputs are enabled; when $\overline{OE}$ is HIGH, the FIFO's outputs are in High Z (high impedance) state.                                                                                                                                           |  |  |  |

| WCLK             | Input           | Write clock: When enabled by $\overline{WEN}$ , the rising edge of WCLK writes data into the FIFO if $\overline{LD}$ is high and into the configuration registers if LD is low.                                                                                                                             |  |  |  |

| RCLK             | Input           | Read clock: When enabled by $\overline{\text{REN}}$ , the rising edge of RCLK reads data from the FIFO memory if $\overline{\text{LD}}$ is high and from the configuration registers if $\overline{\text{LD}}$ is low.                                                                                      |  |  |  |

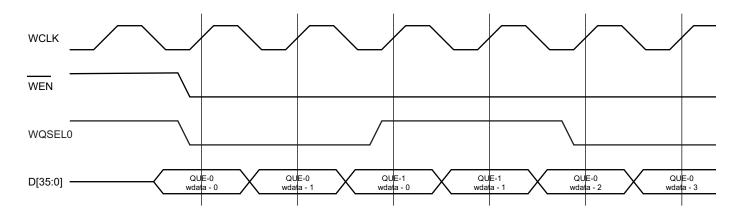

| DVal0            | Output          | Data valid for Queue-0: Active low signal indicating valid data read for Queue-0 from Q[35:0].                                                                                                                                                                                                              |  |  |  |

| DVal1            | Output          | Data valid for Queue-1: Active low signal indicating valid data read for Queue-1 from Q[35:0].                                                                                                                                                                                                              |  |  |  |

| EF               | Output          | Empty flag: When EF is LOW, the Queue is empty. EF is synchronized to RCLK.                                                                                                                                                                                                                                 |  |  |  |

| FF               | Output          | Full flag: When FF is LOW, the Queue is full. FF is synchronized to WCLK.                                                                                                                                                                                                                                   |  |  |  |

| LD               | Input           | Load: When LD is LOW, D[7:0] (Q[7:0]) are written (read) into (from) the configuration registers. When LD is HIGH, D[35:0] (Q[35:0]) are written (read) into (from) the FIFO.                                                                                                                               |  |  |  |

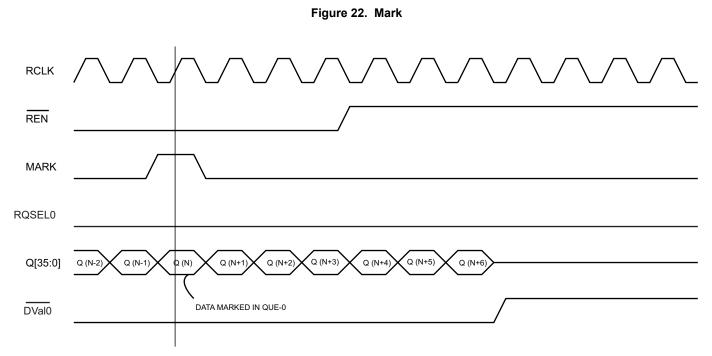

| RT               | Input           | Retransmit: A HIGH pulse on RT resets the internal read pointer to a physical location of the FIFO which is marked by the user (using MARK pin). With every valid read cycle after retransmit, previously accessed data is read and the read pointer is incremented until it is equal to the write pointer. |  |  |  |

| MRS              | Input           | Master reset: MRS initializes the read and write pointers to zero and sets the output register to all zeroes. During Master Reset, the configuration registers are all set to default values and flags are reset.                                                                                           |  |  |  |

| SPI_SCLK         | Input           | Serial clock: A rising edge on SPI_SCLK clocks the serial data present on the SPI_SI input into the offset registers if SPI_SEN is enabled.                                                                                                                                                                 |  |  |  |

| SPI_SI           | Input           | Serial input: Serial input when SPI_SEN is enabled.                                                                                                                                                                                                                                                         |  |  |  |

| SPI_SEN          | Input           | Serial enable: Enables serial loading of programmable flag offsets and configuration registers.                                                                                                                                                                                                             |  |  |  |

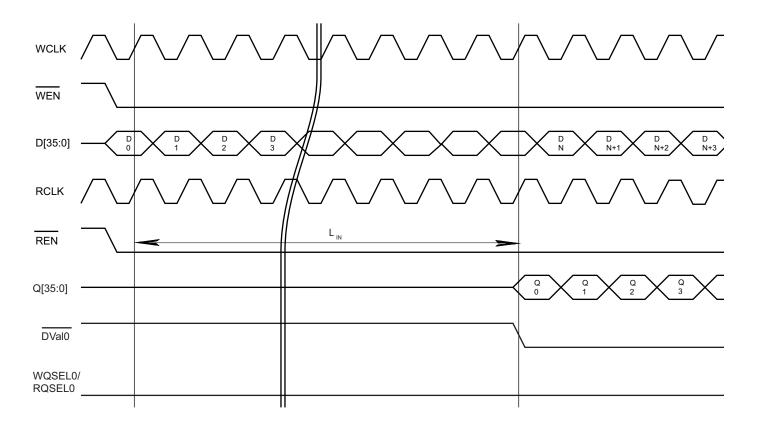

| MARK             | Input           | Mark for retransmit: When this pin is asserted the current location of the read pointer is marked. Any subsequent retransmit operation resets the read pointer to this position.                                                                                                                            |  |  |  |

| MB               | Input           | Mailbox: When asserted the reads and writes happen to flow-through mailbox register.                                                                                                                                                                                                                        |  |  |  |

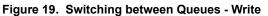

| WQSEL0           | Input           | Write Queue select: select Queue-0 when low and Queue-1 when high.                                                                                                                                                                                                                                          |  |  |  |

| RQSEL0           | Input           | Read Queue select: select Queue-0 when low and Queue-1 when high.                                                                                                                                                                                                                                           |  |  |  |

| ТСК              | Input           | Test clock (TCK) pin for JTAG.                                                                                                                                                                                                                                                                              |  |  |  |

| TRST             | Input           | Reset pin for JTAG.                                                                                                                                                                                                                                                                                         |  |  |  |

| TMS              | Input           | Test mode select (TMS) pin for JTAG.                                                                                                                                                                                                                                                                        |  |  |  |

| TDI              | Input           | Test data in (TDI) pin for JTAG.                                                                                                                                                                                                                                                                            |  |  |  |

| TDO              | Output          | Test data out (TDO) for JTAG.                                                                                                                                                                                                                                                                               |  |  |  |

| PORTSZ [2:0]     | Input           | Port word size select: Port word width select pins (common for read and write ports).                                                                                                                                                                                                                       |  |  |  |

| V <sub>CC1</sub> | Power<br>Supply | Core voltage supply 1: 1.8 V supply voltage                                                                                                                                                                                                                                                                 |  |  |  |

| V <sub>CC2</sub> | Power<br>Supply | Core voltage supply 2: 1.5 V supply voltage                                                                                                                                                                                                                                                                 |  |  |  |

## Pin Definitions (continued)

| Pin Name          | I/O                | Pin Description                                                        |

|-------------------|--------------------|------------------------------------------------------------------------|

| V <sub>CCIO</sub> | Power<br>Supply    | Supply for I/Os.                                                       |

| Vref              | Input<br>Reference | Reference voltage: Reference voltage (regardless of I/O standard used) |

| V <sub>SS</sub>   | Ground             | Ground                                                                 |

| DNU               | -                  | Do not use: These pins need to be left floating.                       |

## Architecture

The CYF1072V, CYF1036V, and CYF1018V are of memory arrays of 72-Mbit, 36-Mbit, and 18-Mbit respectively. The memory organization is user configurable and word sizes can be selected as  $\times 9$ ,  $\times 12$ ,  $\times 16$ ,  $\times 18$ ,  $\times 20$ ,  $\times 24$ ,  $\times 32$ , or  $\times 36$ . The logic blocks to implement FIFO functionality and the associated features are built around these memory arrays.

The input and output data buses have a maximum width of 36 bits configurable through PORTSZ[2:0]. The input data bus goes to an input register and the data flow from the input register to the memory is controlled by th<u>e write</u> logic block. The inputs to the write logic block are W<u>CLK</u>, WEN and WQSEL0. When the writes are enabled through WEN, the data on the input bus is written into the memory array at the rising edge of WCLK. This also increments the write pointer. WQSEL0 selects the Queue for write operation.

Similarly, the output register is connected to the data output bus. Transfer of contents from the memory to the output register is controlled by the read control logic. The inputs to the read control logic include RCLK, REN, OE, RQSEL0, RT and MARK. When reads are enabled by REN and outputs are enabled through OE, the data from the memory pointed by the read pointer is transferred to the output data bus at the rising edge of RCLK along with active low Dval0 or Dval1 based on the Queue number <u>selected</u> using RQSEL0. If the outputs are disabled through OE but the reads enabled, the outputs are in high impedance state, but internally the read pointer is incremented. The MARK signal is used to 'mark' the location from which data is retransmitted when requested.

During write operation, the number of writes performed is always a even number (i.e., minimum write burst length is two and number of writes always a multiple of two), whereas during read operation, the number of reads performed can be even or odd (i.e., minimum read burst length is one).

By default, the FIFO is accessed as a single Queue device. It is possible to divide the whole memory space into 2 equal sized array, and each array can be independently accessed as an independent FIFO. This is like having two independent Queues inside the FIFO instead of entire memory space acting as single Queue FIFO. User can configure the number of Queues by setting the value of D0 of configuration register 3(refer Table 3 on page 9). Table 2 on page 8 shows the value to be set in D0 of configuration register 3 to configure the device in single-Queue or two-Queue mode.

#### **Reset Logic**

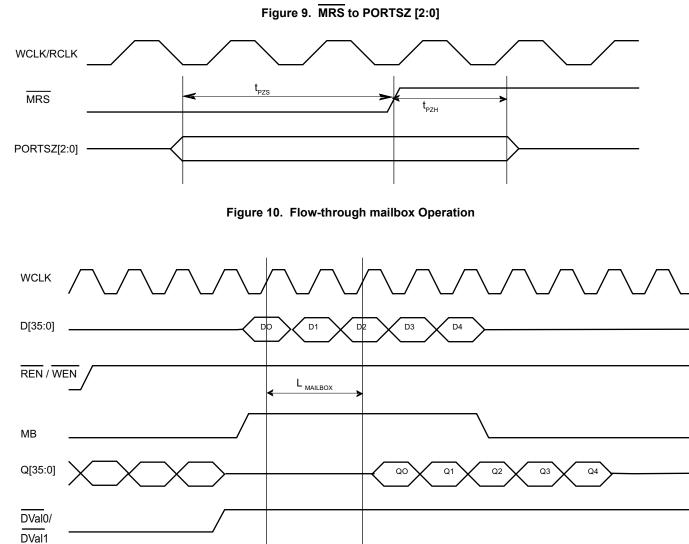

The Master Reset (MRS) initializes the read and write pointers to zero, sets the output registers to all zeros and sets the status of the flags to FF deasserted and EF asserted. MRS also resets the configuration register and the mark address to their default values. MRS affects all the Queues in the FIFO. A MRS is required after power up before accessing the FIFO. After MRS, a minimum latency of 1024 clocks is necessary before the first access. The word size is configured through pins; values of the three PORTSZ pins are latched during rising edge of MRS. After MRS, the device is configured in single Queue mode by default.

#### Flag Operation

This device provides two flag pins to indicate the condition of the FIFO contents.

#### Full Flag

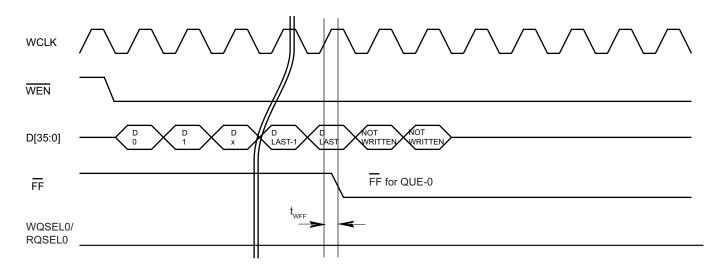

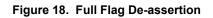

The Full Flag (FF) goes LOW when the device is full. All write operations are ignored whenever FF is LOW regardless of the state of WEN. FF is synchronized to WCLK, that is, it is exclusively updated by each rising edge of WCLK. In 2Q mode, FF indicates the status of the Queue selected by WQSEL0. The worst case assertion latency for Full Flag is four. As the user cannot know that the FIFO is full for four clock cycles, it is possible that user continues writing data during this time. In this case, the four data word written will be stored to prevent data loss and these words have to be read back in order for full flag to get de-asserted. The minimum number of reads required to de-assert full-flag is two and the maximum number of reads required to de-assert full flag is six. The assertion and de-assertion of full flag with associated latencies is explained in Latency Table on page 14.

#### **Empty Flag**

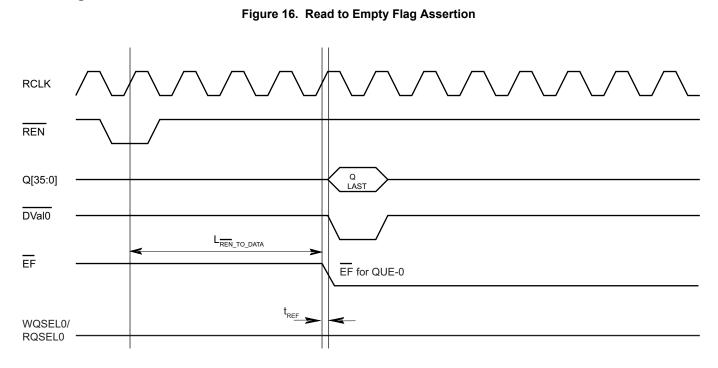

The Empty Flag (EF) goes LOW when the device is empty. Read operations are ignored whenever EF is LOW, regardless of the state of REN. EF is synchronized to RCLK, i.e., it is exclusively updated by each rising edge of RCLK. In 2Q mode, EF indicates the status of the Queue selected by RQSEL0. The assertion and de-assertion of empty flag with associated latencies is explained in Latency Table on page 14.

#### **Retransmit from Mark Operation**

The retransmit feature is useful for transferring packets of data repeatedly. It enables the receipt of data to be acknowledged by the receiver and retransmitted if necessary. The retransmit feature is used when the number of writes equal to or less than the depth of the FIFO has occurred - and at least one word has been read since the last reset cycle. A HIGH pulse on RT resets the internal read pointer to a physical location of the FIFO that is marked by the user (using the MARK pin). In 2-Queue mode the MARK and RT signals are validated with RQSEL0, i.e., Mark or Retransmit function will be performed for the Queue that is selected by RQSEL0. With every valid read cycle after retransmit, previously accessed data is read and the read pointer is incremented until it is equal to the write pointer. Flags are governed by the relative locations of the read and write pointers and are updated during a retransmit cycle. Data written to FIFO after activation of RT are also transmitted. The full depth of the FIFO can be repeatedly retransmitted. To mark a location, the Mark pin is asserted when reading that particular location.

#### Flow-through mailbox Register

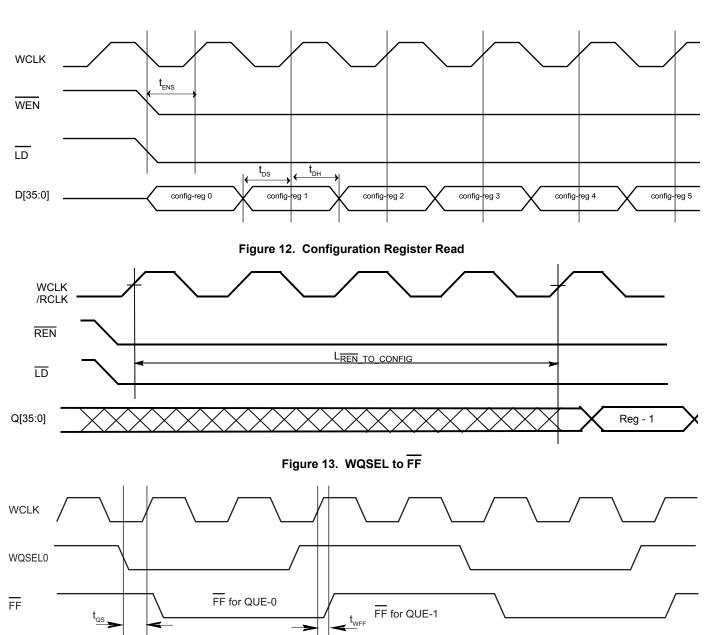

This feature transfers data from input to output directly by bypassing the FIFO sequence. When MB signal is asserted the data present in D[35:0] will be available at Q[35:0] after two WCLK cycles. Normal read and write operations are not allowed during flow-through mailbox operation. Before starting Flow-through mailbox operation FIFO read should be completed to make data valid (DVal0/DVal1) high in order to avoid data loss from FIFO. The width of flow-through mailbox register always corresponds to port size.

#### **Selecting Word Sizes**

The word sizes are configured based <u>on the</u> logic levels on the PORTSZ pins during the master reset (MRS) cycle only (latched on low to high edge). The port size cannot be changed during normal mode of operation and these pins are ignored. Table 1. explains the pins of D[35:0] and Q[35:0] that will have valid data in modes where the word size is less than × 36. If word size is less than × 36, the unused output pins are tri-stated by the device and unused input pins will be ignored by the internal logic. The pins with valid data input D[N:0] and output Q[N:0] is given in Table 1.

Data valid (Dval0, Dval1) are active low signals provided for easy

# valid data on Q bus for either Queue-0 or Queue-1. This helps to capture the data without keeping track of REN and RQSEL0 to data output latency. These signals also help to capture the output data when write and read operations are performed continuously at different frequencies by indicating when valid data is read out at the output port Q[35:0].

## **Power Up**

The device becomes functional after V<sub>CC1</sub>, V<sub>CC2</sub>, V<sub>CCI0</sub>, and Vref attain minimum stable voltage required as given in Recommended DC Operating Conditions on page 13. The device can be accessed  $t_{PU}$  time after these supplies attain the minimum required level

(see Switching Characteristics on page 15). There is no power sequencing requirement for the device.

## capture of output data. When a read operation is performed, the DVal0/DVal1 signal goes low along with output data indicating

#### Table 1. Word Size Selection

Data Valid Signal

| PORTSZ[2:0] | Word Size | Active input data pins D[X:0] | Active output data pins Q[X:0] |

|-------------|-----------|-------------------------------|--------------------------------|

| 000         | × 9       | D[8:0]                        | Q[8:0]                         |

| 001         | × 12      | D[11:0]                       | Q[11:0]                        |

| 010         | × 16      | D[15:0]                       | Q[15:0]                        |

| 011         | × 18      | D[17:0]                       | Q[17:0]                        |

| 100         | × 20      | D[19:0]                       | Q[19:0]                        |

| 101         | × 24      | D[23:0]                       | Q[23:0]                        |

| 110         | × 32      | D[31:0]                       | Q[31:0]                        |

| 111         | × 36      | D[35:0]                       | Q[35:0]                        |

#### Table 2. Multi-Queue Configuration

| operating mode        | RQSEL0/WQSEL0 | Queue Number Selected |

|-----------------------|---------------|-----------------------|

| 1Q mode               | 0             | 0                     |

| register $0x3[0] = 0$ | 1             | invalid               |

| 2Q mode               | 0             | 0                     |

| register 0x3[0] = 1   | 1             | 1                     |

#### **Read Skip Operation**

As mentioned in Architecture on page 7, during a read operation, if the outputs are disabled by having the OE high, the read data does not appear on the output bus; however, the read pointer is incremented.

#### **Multi-Queue Operation**

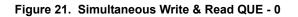

In general, the entire memory space is accessed as a First In First Out (FIFO) order for the write and read operation. In this case, the entire memory space is called a single Queue. For example, for 72M device, the entire memory space is available as a single Queue FIFO operation.

In multi Queue mode, the entire memory space is divided into equal sized memory array and each individual memory array can be accessed as an independent FIFO based on additional control signals. These independent memory arrays are called as Queues. For example, when 72M device, is configured into two Queue mode, the entire memory space of 72M is divided into two 36M memory array called as Queue-0 and Queue-1. These Queues can be accessed independently as a FIFO by selecting the Queue select signals WQSEL0 and RQSEL0. In this way, two Queues can be created for a given device where data can be stored independently and read out independently.

#### Table 3. Configuration Registers

| ADDR | Configuration Register | Default   | Bit [7]         | Bit [6] | Bit [5] | Bit [4] | Bit [3] | Bit [2] | Bit [1] | Bit [0] |

|------|------------------------|-----------|-----------------|---------|---------|---------|---------|---------|---------|---------|

| 0x1  | Reserved               | 0x00      | Х               | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

| 0x2  | Reserved               | 0x00      | Х               | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

| 0x3  | Number of Queues       | 0x00      | Х               | Х       | Х       | Х       | Х       | Х       | Х       | D0      |

| 0x4  | Reserved               | 0x7F      | Х               | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

| 0x5  | Reserved               | 0x00      | Х               | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

| 0x6  | Reserved               | 0x00      | Х               | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

| 0x7  | Reserved               | 0x7F      | Х               | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

| 0x8  | Reserved               | 0x00      | Х               | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

| 0x9  | Reserved               | 0x00      | Х               | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

| 0xA  | Fast CLK Bit Register  | 1XXXXXXXb | Fast<br>CLK bit | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

#### Table 4. Writing and Reading Configuration Registers in Parallel Mode

| SPI_SEN | LD | WEN | REN | WCLK                                                                       | RCLK                                                                    | SPI_SCLK | Operation                                     |

|---------|----|-----|-----|----------------------------------------------------------------------------|-------------------------------------------------------------------------|----------|-----------------------------------------------|

| 1       | 0  | 0   | 1   | ↑ First risin <u>g edg</u> e<br>bec <u>ause</u> both LD and<br>WEN are low | Х                                                                       | х        | Parallel write to first register              |

| 1       | 0  | 0   | 1   | $\uparrow$ Second rising edge                                              | Х                                                                       | Х        | Parallel write to second register             |

| 1       | 0  | 0   | 1   | $\uparrow$ Third rising edge                                               | Х                                                                       | Х        | Parallel write to third register              |

| 1       | 0  | 0   | 1   | $\uparrow$ Fourth rising edge                                              | Х                                                                       | Х        | Parallel write to fourth register             |

| 1       | 0  | 0   | 1   | •                                                                          | Х                                                                       | Х        | •                                             |

| 1       | 0  | 0   | 1   | •                                                                          | Х                                                                       | Х        | •                                             |

| 1       | 0  | 0   | 1   | •                                                                          | Х                                                                       | Х        | •                                             |

| 1       | 0  | 0   | 1   | $\uparrow$ Tenth rising edge                                               | Х                                                                       | Х        | Parallel write to tenth register              |

| 1       | 0  | 0   | 1   | $\uparrow$ Eleventh rising edge                                            | Х                                                                       | х        | Parallel write to first register (roll back)  |

| 1       | 0  | 1   | 0   | Х                                                                          | ↑ First r <u>ising</u> ed <u>ge</u><br>since both LD and REN<br>are low | х        | Parallel read from first register             |

| 1       | 0  | 1   | 0   | Х                                                                          | ↑ Second rising edge                                                    | Х        | Parallel read from second register            |

| 1       | 0  | 1   | 0   | Х                                                                          | $\uparrow$ Third rising edge                                            | Х        | Parallel read from third register             |

| 1       | 0  | 1   | 0   | Х                                                                          | $\uparrow$ Fourth rising edge                                           | Х        | Parallel read from fourth register            |

| 1       | 0  | 1   | 0   | Х                                                                          | •                                                                       | Х        | •                                             |

| 1       | 0  | 1   | 0   | Х                                                                          | •                                                                       | Х        | •                                             |

| 1       | 0  | 1   | 0   | Х                                                                          | •                                                                       | Х        | •                                             |

| 1       | 0  | 1   | 0   | Х                                                                          | ↑ Tenth rising edge                                                     | Х        | Parallel read from tenth register             |

| 1       | 0  | 1   | 0   | Х                                                                          | $\uparrow$ Eleventh rising edge                                         | Х        | Parallel read from first register (roll back) |

| 1       | Х  | 1   | 1   | Х                                                                          | Х                                                                       | Х        | No operation                                  |

| SPI_SEN | LD | WEN | REN | WCLK          | RCLK          | SPI_SCLK | Operation             |

|---------|----|-----|-----|---------------|---------------|----------|-----------------------|

| Х       | 1  | 0   | Х   | ↑ Rising edge | Х             | Х        | Write to FIFO memory  |

| Х       | 1  | Х   | 0   | Х             | ↑ Rising edge | Х        | Read from FIFO memory |

| 0       | 0  | Х   | 1   | Х             | Х             | Х        | Illegal operation     |

#### Table 4. Writing and Reading Configuration Registers in Parallel Mode (continued)

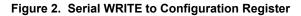

Table 5. Writing into Configuration Registers in Serial Mode

| SPI_SEN | LD | WEN | REN | WCLK          | RCLK          | SCLK          | Operation                                                                                                                                                           |

|---------|----|-----|-----|---------------|---------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 1  | Х   | Х   | Х             | Х             | ↑ Rising edge | Each rising of the SCLK clocks<br>in one bit from the SI (Serial In).<br>Any of the 10 registers can be<br>addressed and written to,<br>following the SPI protocol. |

| Х       | 1  | 0   | Х   | ↑ Rising edge | Х             | Х             | Parallel write to FIFO memory.                                                                                                                                      |

| Х       | 1  | Х   | 0   | Х             | ↑ Rising edge | х             | Parallel read from FIFO memory.                                                                                                                                     |

| 1       | 0  | 1   | 1   | Х             | Х             | Х             | This corresponds to parallel mode (refer to Table 4).                                                                                                               |

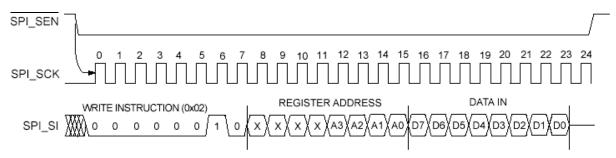

#### Width Expansion Configuration

The width of CYF1072V can be expanded to provide word widths greater than 36 bits. During width expansion mode, all control line inputs are common and all flags are available. Empty (Full) flags are created by ANDing the Empty (Full) flags of every FIFO.

This technique avoids reading data from or writing data to the FIFO that is "staggered" by one clock cycle due to the variations in skew between RCLK and WCLK. Figure 3 on page 11 demonstrates a 72 bit-word width by using two 36-bit word CYF1072Vs.

#### Figure 3. Using Two CYF1072V for Width Expansion

#### Memory Organization for Different Port Sizes

The 72-Mbit memory has different organization for different port sizes. Table 6 shows the depth of the FIFO for all port sizes.

Note that for all port sizes, four to eight locations are not available for writing the data and are used to safeguard against false synchronization of empty and full flags.

| PORTSZ[2:0] | Word Size | FIFO Depth | Memory Size |

|-------------|-----------|------------|-------------|

| 000         | × 9       | 8 Meg      | 72 Mbit     |

| 001         | × 12      | 4 Meg      | 48 Mbit     |

| 010         | × 16      | 4 Meg      | 64 Mbit     |

| 011         | × 18      | 4 Meg      | 72 Mbit     |

| 100         | × 20      | 2 Meg      | 40 Mbit     |

| 101         | × 24      | 2 Meg      | 48 Mbit     |

| 110         | × 32      | 2 Meg      | 64 Mbit     |

| 111         | × 36      | 2 Meg      | 72 Mbit     |

#### Table 6. Word Size Selection

The memory size mentioned is when the device is configured in single-Queue mode.

#### **Read/Write Clock Requirements**

The read and write clocks must satisfy the following requirements:

- Both read (RCLK) and write (WCLK) clocks should be free-running.

- The clock frequency for both clocks should be between the minimum and maximum range given in Switching Characteristics on page 15.

■ The ratio of RCLK to WCLK must be in the range of 0.5 to 2.

The device uses internal PLL to achieve high performance. Whenever there is change in the frequency of the clock, the device takes  $t_{PLL}$  time to synchronize with the input clock. (see Switching Characteristics on page 15). The PLL requires re-synchronization when there is change in the frequency of either WCLK or RCLK or when master reset is asserted.

For proper FIFO operation, the device must determine which of the input clocks – RCLK or WCLK – is faster. This is evaluated by using counters after the MRS cycle. The device uses two 10-bit counters inside (one running on RCLK and other on WCLK), which count 1,024 cycles of read and write clock after MRS. The clock of the counter which reaches its terminal count first is used as master clock inside the FIFO.

When there is change in the relative frequency of RCLK and WCLK during normal operation of FIFO, user can specify it by using "Fast CLK bit" in the configuration register (0xA).

- "1" indicates  $f_{req}$  (WCLK) >  $f_{req}$  (RCLK)

- "0" indicates f<sub>req</sub> (WCLK) < f<sub>req</sub> (RCLK)

The result of counter evaluated frequency is available in this register bit. User can override the counter evaluated frequency for faster clock by changing this bit.

Whenever there is a change in this bit value, user must wait  $t_{PLL}$  time before issuing the next read or write to FIFO.

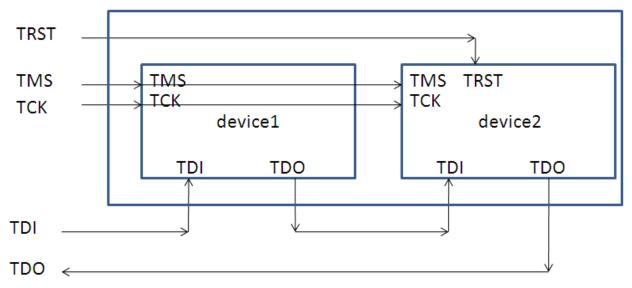

#### JTAG operation

CYF1072V has two devices connected internally in a JTAG chain as shown in Figure 4 on page 12.

Table 7 shows the IR register length and device ID.

#### Table 7. JTAG IDCODES

|          | IR Register length | Device ID (HEX) | Bypass register length |

|----------|--------------------|-----------------|------------------------|

| Device-1 | 3                  | "Ignore"        | 1                      |

| Device-2 | 8                  | 1E3261CF        | 1                      |

For boundary scan, device-1 should be in bypass mode.

Table 8 and Table 9 shows the JTAG instruction set for devices 1 and 2.

#### Table 8. JTAG Instructions

| Device-1 | Opcode (Binary) |

|----------|-----------------|

| BYPASS   | 111             |

#### Table 9. JTAG Instructions

| Device-2       | Opcode (HEX) |

|----------------|--------------|

| EXTEST         | 00           |

| HIGHZ          | 07           |

| SAMPLE/PRELOAD | 01           |

| BYPASS         | FF           |

| IDCODE         | 0F           |

## **Maximum Ratings**

Exceeding maximum ratings may impair the useful life of the device. These user guidelines are not tested.

| Storage temperature (without bias) –65 °C to +150 °C                    |

|-------------------------------------------------------------------------|

| Ambient temperature with power applied55 °C to +125 °C                  |

| Core supply voltage 1 (V_{CC1}) to ground potential0.3 V to 2.5 V       |

| Core supply voltage 2 (V $_{CC2}$ ) to ground potential–0.3 V to 1.65 V |

| Latch-up current>100mA                                                  |

| I/O port supply voltage (V <sub>CCIO</sub> )–0.3 V to 3.7 V        |  |

|--------------------------------------------------------------------|--|

| Voltage applied to I/O pins–0.3 V to 3.75 V                        |  |

| Output current into outputs (LOW)                                  |  |

| Static discharge voltage<br>(per MIL–STD–883, Method 3015)> 2001 V |  |

## **Operating Range**

| Range      | Ambient Temperature |

|------------|---------------------|

| Industrial | –40 °C to +85 °C    |

## **Recommended DC Operating Conditions**

| Parameter <sup>[2]</sup> | Description                                           | Min      | Тур   | Max  | Unit  |   |

|--------------------------|-------------------------------------------------------|----------|-------|------|-------|---|

| V <sub>CC1</sub>         | Core supply voltage 1                                 | 1.70     | 1.80  | 1.90 | V     |   |

| V <sub>CC2</sub>         | Core supply voltage 2                                 |          | 1.425 | 1.5  | 1.575 | V |

| V <sub>REF</sub>         | Reference voltage (irrespective of I/O standard used) |          | 0.7   | 0.75 | 0.8   | V |

| V <sub>CCIO</sub>        | I/O supply voltage, read and write banks.             | LVCMOS33 | 3.00  | 3.30 | 3.60  | V |

|                          |                                                       | LVCMOS18 | 1.70  | 1.8  | 1.90  | V |

## **Electrical Characteristics**

| Parameter        | Description                                     | Conditions                                                             | Min | Тур | Мах | Unit |

|------------------|-------------------------------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>cc</sub>  | Active current                                  | V <sub>CC1</sub> = V <sub>CC1MAX</sub>                                 | -   | -   | 300 | mA   |

|                  |                                                 | V <sub>CC2</sub> = V <sub>CC2MAX</sub> ,<br>All I/O switching, 100 MHz | -   | -   | 500 | mA   |

|                  |                                                 | V <sub>CCIO</sub> = V <sub>CCIOMAX</sub><br>(All outputs disabled)     | -   | -   | 100 | mA   |

| I <sub>I</sub>   | Input pin leakage current                       | V <sub>IN</sub> = V <sub>CCIOmax</sub> to 0 V                          | -15 | -   | 15  | μA   |

| I <sub>OZ</sub>  | I/O pin leakage current                         | V <sub>O</sub> = V <sub>CCIOmax</sub> to 0 V                           | -15 | -   | 15  | μA   |

| C <sub>P</sub>   | Capacitance for TMS and TCK                     | -                                                                      | -   | -   | 16  | pF   |

| C <sub>PIO</sub> | Capacitance for all I/Os apart from TMS and TCK | -                                                                      | _   | -   | 8   | pF   |

## I/O Characteristics

| 1/O standard | Nominal I/O       | Input Voltage (V)     |                       | Output voltage (V)    |                          | Output Current (mA)   |                       |

|--------------|-------------------|-----------------------|-----------------------|-----------------------|--------------------------|-----------------------|-----------------------|

| I/O standard | supply<br>voltage | V <sub>IL</sub> (max) | V <sub>IH</sub> (min) | V <sub>OL</sub> (max) | V <sub>OH</sub> (min)    | l <sub>OL</sub> (max) | l <sub>OH</sub> (max) |

| LVCMOS33     | 3.3 V             | 0.80                  | 2.20                  | 0.45                  | 2.40                     | 24                    | 24                    |

| LVCMOS18     | 1.8 V             | 30% V <sub>CCIO</sub> | 65% V <sub>CCIO</sub> | 0.45                  | V <sub>CCIO</sub> – 0.45 | 16                    | 16                    |

## Latency Table

| Latency Parameter         | Number of cycles     | Details                                                                                                                            |

|---------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| LFF_ASSERT                | Min = 0<br>Max = 4   | Last data write to FF going low                                                                                                    |

| L <sub>EF_ASSERT</sub>    | 0                    | Last data read to EF going low                                                                                                     |

| L <sub>RQSEL_CHANGE</sub> | 1                    | Minimum RCLK cycles before RQSEL0 can change                                                                                       |

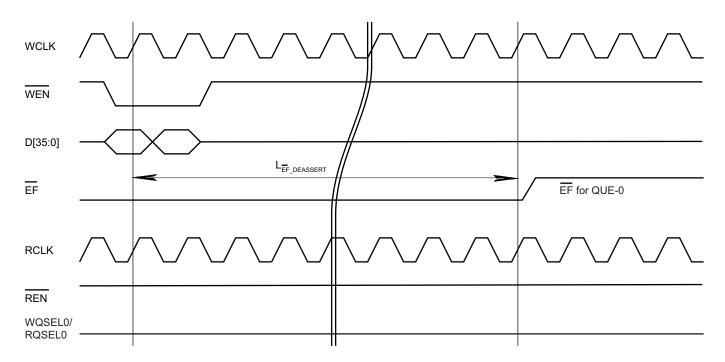

| L <sub>WQSEL_CHANGE</sub> | 2                    | Minimum WCLK cycles before WQSEL0 can change                                                                                       |

| L <sub>MAILBOX</sub>      | 2                    | Latency from write port to read port when MB = 1 (w.r.t WCLK)                                                                      |

| LREN_TO_DATA              | 4                    | Latency when REN is asserted low to first data output from FIFO                                                                    |

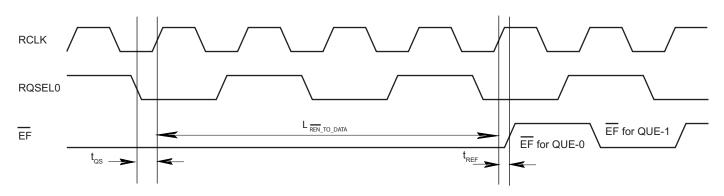

| LREN_TO_CONFIG            | 4                    | Latency when $\overline{\text{REN}}$ is asserted along with $\overline{\text{LD}}$ to first data read from configuration registers |

| LFF_DEASSERT              | 7                    | Read to FF going high                                                                                                              |

| L <sub>RT_TO_REN</sub>    | 9                    | RT 5th cycle to REN going low for read                                                                                             |

| L <sub>RT_TO_DATA</sub>   | Min = 20<br>Max = 23 | RT 5th cycle to valid data on Q[35:0]                                                                                              |

| L <sub>IN</sub>           | Min = 8<br>Max = 29  | Initial latency for data read after FIFO goes empty during simultaneous read/write                                                 |

| L <sub>EF_DEASSERT</sub>  | Min = 6<br>Max = 27  | Write to EF going high                                                                                                             |

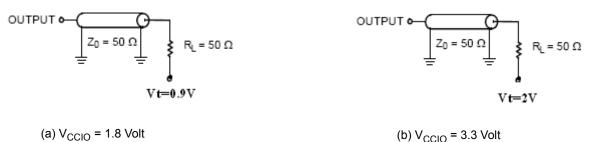

#### Figure 5. AC Test Load Conditions

(c) All Input Pulses

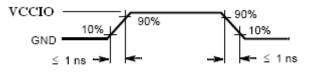

## Switching Characteristics

Over the operating Range

| Devenueter             | Description                                        |              |     | -100  |                |

|------------------------|----------------------------------------------------|--------------|-----|-------|----------------|

| Parameter              | Description                                        |              |     | Max   | Unit           |

| t <sub>PU</sub>        | Power-up time after all supplies reach minimum val | ue           | -   | 2     | ms             |

| t <sub>S</sub>         | Clock cycle frequency                              | 3.3 V LVCMOS | 24  | 100   | MHz            |

| t <sub>S</sub>         | Clock cycle frequency                              | 1.8 V LVCMOS | 24  | 100   | MHz            |

| t <sub>A</sub>         | Data access time                                   |              | -   | 10    | ns             |

| t <sub>CLK</sub>       | Clock cycle time                                   |              | 10  | 41.67 | ns             |

| t <sub>CLKH</sub>      | Clock high time                                    |              | 4.5 | -     | ns             |

| t <sub>CLKL</sub>      | Clock low time                                     |              | 4.5 | -     | ns             |

| t <sub>DS</sub>        | Data setup time                                    |              | 3   | -     | ns             |

| t <sub>DH</sub>        | Data hold time                                     |              | 3   | -     | ns             |

| t <sub>QS</sub>        | RQSEL0 and WQSEL0 setup time                       |              | 3   | -     | ns             |

| t <sub>QH</sub>        | RQSEL0 and WQSEL0 hold time                        |              | 3   | -     | ns             |

| t <sub>ENS</sub>       | Enable setup time                                  |              | 3   | -     | ns             |

| t <sub>ENH</sub>       | Enable hold time                                   |              | 3   | -     | ns             |

| t <sub>ENS SI</sub>    | Setup time for SPI_SI and SPI_SEN pin              |              | 5   | -     | ns             |

| t <sub>ENH_SI</sub>    | Hold time for SPI_SI and SPI_SEN pin               |              | 5   | -     | ns             |

| t <sub>RATE_SPI</sub>  | Frequency of SPI_SCLK                              |              | -   | 25    | MHz            |

| t <sub>RS</sub>        | Reset pulse width                                  |              | 100 | -     | ns             |

| t <sub>PZS</sub>       | Port size select to MRS setup time                 |              | 25  | -     | ns             |

| t <sub>PZH</sub>       | MRS to port size select hold time                  |              | 25  | -     | ns             |

| t <sub>RSF</sub>       | Reset to flag output time                          |              | -   | 50    | ns             |

| t <sub>PRT</sub>       | Retransmit pulse width                             |              | 5   | -     | RCLK<br>cycles |

| t <sub>OLZ</sub>       | Output enable to output in Low Z                   |              | 4   | 15    | ns             |

| t <sub>OE</sub>        | Output enable to output valid                      |              | _   | 15    | ns             |

| t <sub>OHZ</sub>       | Output enable to output in High Z                  |              | _   | 15    | ns             |

| t <sub>WFF</sub>       | Write clock to FF                                  |              | -   | 9     | ns             |

| t <sub>REF</sub>       | Read clock to EF                                   |              | -   | 9     | ns             |

| t <sub>PLL</sub>       | Time required to synchronize PLL                   |              | -   | 1024  | cycles         |

| t <sub>RATE_JTAG</sub> | JTAG TCK cycle time                                |              | 100 | -     | ns             |

| t <sub>S_JTAG</sub>    | Setup time for JTAG TMS,TDI                        |              | 8   | -     | ns             |

| t <sub>H_JTAG</sub>    | Hold time for JTAG TMS,TDI                         |              | 8   | -     | ns             |

| t <sub>CO_JTAG</sub>   | JTAG TCK low to TDO valid                          |              | -   | 20    | ns             |

## **Switching Waveforms**

Figure 14. RQSEL0 to EF

Figure 15. Write to Empty Flag De-assertion

Figure 17. Full Flag Assertion

Figure 23. Retransmit

## **Ordering Information**

| Speed<br>(MHz) | Ordering Code       | Package<br>Diagram | Package Type                                                   | Operating<br>Range |

|----------------|---------------------|--------------------|----------------------------------------------------------------|--------------------|

| 100            | CYF1018V33L-100BGXI | 51-85167           | 209-ball fine-pitch ball grid array (FBGA) (14 × 22 × 1.76 mm) | Industrial         |

|                | CYF1036V33L-100BGXI |                    |                                                                |                    |

|                | CYF1072V33L-100BGXI |                    |                                                                |                    |

|                | CYF1018V18L-100BGXI |                    |                                                                |                    |

|                | CYF1036V18L-100BGXI |                    |                                                                |                    |

|                | CYF1072V18L-100BGXI |                    |                                                                |                    |

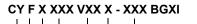

#### **Ordering Code Definitions**

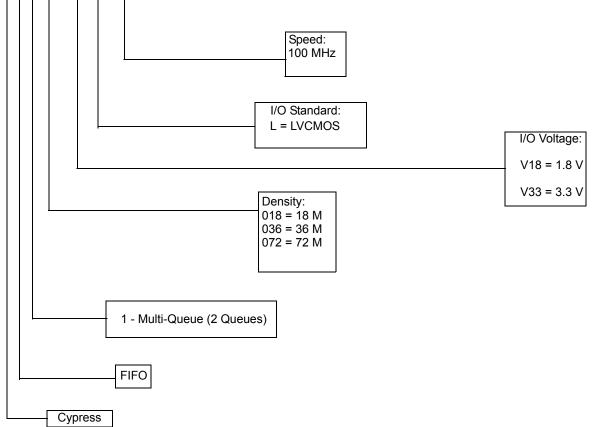

## Package Diagram

Figure 24. 209-ball FBGA (14 × 22 × 1.76 mm) BB209A, 51-85167

## Acronyms

| Acronym | Description                                            |  |  |  |

|---------|--------------------------------------------------------|--|--|--|

| EF      | empty flag                                             |  |  |  |

| FF      | full flag                                              |  |  |  |

| FIFO    | first in first out                                     |  |  |  |

| I/O     | input/output                                           |  |  |  |

| FBGA    | fine-pitch ball grid array                             |  |  |  |

| JTAG    | joint test action group                                |  |  |  |

| LVCMOS  | low voltage complementary metal oxide<br>semiconductor |  |  |  |

| MB      | mailbox                                                |  |  |  |

| MRS     | master reset                                           |  |  |  |

| OE      | output enable                                          |  |  |  |

| RCLK    | read clock                                             |  |  |  |

| REN     | read enable                                            |  |  |  |

| RQSEL0  | read queue select                                      |  |  |  |

| SCLK    | serial clock                                           |  |  |  |

| TDI     | test data in                                           |  |  |  |

| TDO     | test data out                                          |  |  |  |

| тск     | test clock                                             |  |  |  |

| TMS     | test mode select                                       |  |  |  |

| WCLK    | write clock                                            |  |  |  |

| WEN     | write enable                                           |  |  |  |

| WQSEL0  | write queue select                                     |  |  |  |

| QUE-0   | queue number 0                                         |  |  |  |

| QUE-1   | queue number 1                                         |  |  |  |

## **Document Conventions**

#### **Units of Measure**

| Symbol | Unit of Measure |  |  |

|--------|-----------------|--|--|

| °C     | degree Celsius  |  |  |

| MHz    | megahertz       |  |  |

| μA     | microampere     |  |  |

| mA     | milliampere     |  |  |

| mm     | millimeter      |  |  |

| ms     | millisecond     |  |  |

| ns     | nanosecond      |  |  |

| Ω      | ohm             |  |  |

| pF     | picofarad       |  |  |

| V      | volt            |  |  |

| W      | watt            |  |  |

## **Document History Page**

|      | Document Title: CYF1018V/CYF1036V/CYF1072V, 18/36/72-Mbit Programmable 2-Queue FIFOs<br>Document Number: 001-68321 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Rev. | ECN No.                                                                                                            | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| **   | 3209860                                                                                                            | SIVS               | 03/30/2011         | New data sheet                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| *A   | 3353401                                                                                                            | AJU                | 08/26/2011         | Updated Package Diagram.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| *В   | 3387127                                                                                                            | AJU                | 09/28/2011         | Updated Pin Diagram for CYF1XXXV (Added Note 1 and referred the same<br>note in DNU in ball U6).<br>Updated Multi-Queue Operation (Updated Table 4 (WCLK column in first row)).<br>Updated Recommended DC Operating Conditions (Added Note 2 and referred<br>the same note in Parameter column).<br>Updated Switching Waveforms (Removed the numbers in Figure 10,<br>Figure 14, Figure 16, and Figure 20). |  |  |  |

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products Automotive cypress.com/go/automotive Clocks & Buffers cypress.com/go/clocks Interface cypress.com/go/interface Lighting & Power Control cypress.com/go/powerpsoc cypress.com/go/plc cypress.com/go/memory Memory **Optical & Image Sensing** cypress.com/go/image **PSoC** cypress.com/go/psoc Touch Sensing cypress.com/go/touch **USB** Controllers cypress.com/go/USB Wireless/RF cypress.com/go/wireless

#### **PSoC Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation, 2011. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction of failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

#### Document Number: 001-68321 Rev. \*B

Revised September 28, 2011

Page 28 of 28

All products and company names mentioned in this document may be the trademarks of their respective holders.