V1.0 July 2009

# TDA 5150 Multichannel / Multiband Transmitter

Multichannel / Multiband RF Transmitter for 300-928 MHz bands

On-chip, high resolution fractional-N synthesizer and Sigma-Delta modulator with ASK, FSK, GFSK options

# Wireless Control

Never stop thinking.

Edition July 2009 Published by Infineon Technologies AG, Am Campeon 1 - 12 85579 Neubiberg, Germany © 2007 Infineon Technologies AG

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions, and prices, please contact the nearest Infineon Technologies Office in Germany or the Infineon Technologies Companies and Infineon Technologies Representatives worldwide (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies Components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| TDA 5150<br>Revision History: |                           | V1.0 |

|-------------------------------|---------------------------|------|

| Previous Version:             | V0.94 issued January 2009 |      |

|                               | New issue                 |      |

|                               |                           |      |

|                               |                           |      |

|                               |                           |      |

|                               |                           |      |

|                               |                           |      |

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: wirelesscontrol@infineon.com

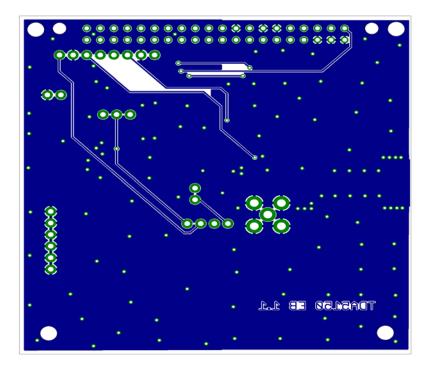

#### **Table of Contents**

| Page |

|------|

|------|

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.5.1<br>1.5.2<br>1.5.3<br>1.5.4<br>1.5.5<br>1.5.6<br>1.5.7                                                                             | Product Description<br>Overview<br>Features<br>Applications<br>Order Information<br>Key Features overview<br>Typical Application Circuit<br>Sigma-Delta fractional-N PLL with High Resolution<br>Reduction of Spurs and Occupied Bandwidth<br>Asynchronous and Synchronous Transmission<br>Integrated Data Encoder<br>Fail-Safe Mechanism<br>TESEUS - Configuration and Evaluation Tool                                                                                                                                                                                                                                                    | · 6<br>· 7<br>· 7<br>· 7<br>· 7<br>· 7<br>· 8<br>· 9<br>· 9<br>· 10<br>10                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.2.1<br>2.4.2.2<br>2.4.2.3<br>2.4.3<br>2.4.3.1<br>2.4.3.2<br>2.4.3.3<br>2.4.3.4<br>2.4.3.5<br>2.4.4<br>2.4.4.1<br>2.4.4.2 | <b>TDA 5150 Functional Description</b> PIN Configuration, Pin-out         Pin Definition and Pin Functionality         Functional Block Diagram         Functional Description         Special Function Registers         Power Supply Circuit         Brownout Detector         Low Battery Detector         SFRs related to Supply Voltage monitoring         Digital Control (3-wire SPI Bus)         SPI XOR Checksum         Command Byte Structure         Transmit Command         Timing Diagrams         Data Encoder         PRBS9 Generator, Data Scrambler         SFRs related to Transmitter Configuration and Data Encoding | 12<br>12<br>17<br>18<br>18<br>19<br>20<br>21<br>21<br>21<br>23<br>24<br>25<br>26<br>28<br>29 |

| 2.4.5<br>2.4.5.1<br>2.4.5.2<br>2.4.5.3<br>2.4.6<br>2.4.6.1<br>2.4.6.2<br>2.4.6.3<br>2.4.6.4<br>2.4.6.5                                                                                 | Crystal Oscillator and Clock Divider<br>The Bit-Rate Generator<br>The Clock Output<br>SFRs related to Crystal Oscillator and Clock Divide<br>Sigma-Delta fractional-N PLL Block<br>Fractional Spurs<br>Voltage Controlled Oscillator (VCO)<br>Loop Filter Bandwidth<br>PLL Dividers, RF Carrier Frequency<br>SFRs related to Sigma-Delta fractional-N PLL Block                                                                                                                                                                                                                                                                            | 33<br>35<br>35<br>36<br>36<br>37<br>38                                                       |

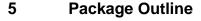

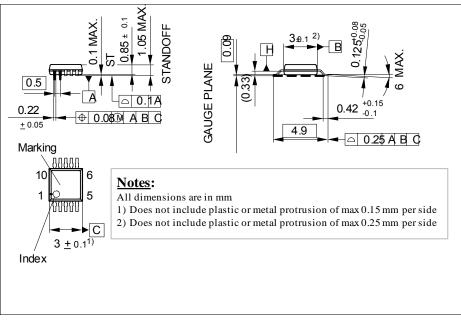

| 5                                      | Package Outline                                                                                                           | 105                   |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|

| <b>4</b><br>4.1<br>4.2<br>4.2.1<br>4.3 | Electrical Characteristics<br>Absolute Maximum Ratings<br>Operating Range<br>AC/DC Characteristics<br>SPI Characteristics | 97<br>98<br>99<br>103 |

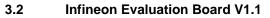

| <b>3</b><br>3.1<br>3.2                 | Applications                                                                                                              | 88                    |

| 2.5<br>2.5.1<br>2.5.2                  | Digital Control (SFR Registers)<br>SFR Register List<br>SFR Detailed Descriptions                                         | 64<br>68              |

| 2.4.11.4                               | Channel Hopping                                                                                                           | 63                    |

| 2.4.11.2                               | Synchronous Transmission                                                                                                  |                       |

| 2.4.11.1                               | Asynchronous Transmission                                                                                                 |                       |

| 2.4.11                                 | RF Data Transmission                                                                                                      |                       |

| 2.4.10.3                               | SFRs related to Supply Voltage monitoring                                                                                 |                       |

| 2.4.10.2                               | Low Battery Monitor                                                                                                       |                       |

| 2.4.10.1                               | Fail-Safe Flags                                                                                                           |                       |

| 2.4.10                                 | Fail-Safe Mechanism and Status Register                                                                                   |                       |

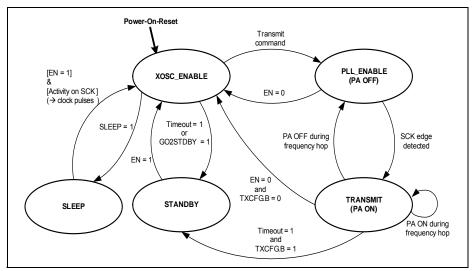

| 2.4.9.6                                | SFRs related to Operating Modes                                                                                           | 56                    |

| 2.4.9.5                                | PLL_ENABLE Mode                                                                                                           |                       |

| 2.4.9.4                                | XOSC_ENABLE Mode                                                                                                          |                       |

| 2.4.9.3                                | TRANSMIT Mode                                                                                                             |                       |

| 2.4.9.2                                | STANDBY Mode (Data Retention Mode)                                                                                        |                       |

| 2.4.9                                  | SLEEP Mode                                                                                                                |                       |

| 2.4.0.0                                | Operating Modes                                                                                                           |                       |

| 2.4.8.5                                | SFRs related to RF Power Amplifier and ASK Modulator                                                                      |                       |

| 2.4.8.4<br>2.4.8.5                     | Antenna Tuning<br>Fail-Safe PA Switch Off                                                                                 |                       |

| 2.4.8.3                                |                                                                                                                           |                       |

| 2.4.8.2                                | ASK Modulation and ASK Sloping                                                                                            |                       |

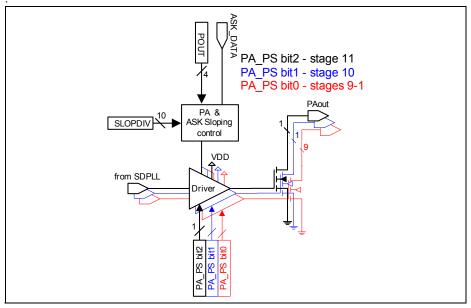

| 2.4.8.1                                | PA Output Power Programming                                                                                               |                       |

| 2.4.8                                  | Power Amplifier, ASK Modulator                                                                                            |                       |

| 2.4.7.1                                | SFRs related to digital FSK / GFSK Modulator                                                                              |                       |

| 2.4.7                                  | Digital FSK/GFSK Modulator                                                                                                | 40                    |

# 1 Product Description

### 1.1 Overview

The TDA 5150 is a low cost and easy to implement, multi-channel ASK/FSK/GFSK RF transmitter for the 300-320 MHz, 425-450 MHz, 863 - 928 MHz frequency bands with low power consumption and RF-output power of up to +10 dBm.

The IC offers a high level of integration and needs only a few external components, such as a crystal, blocking capacitors and the necessary matching elements between the power amplifier output and the antenna.

On-chip antenna tuning capacitors are implemented.

An integrated high-resolution sigma-delta fractional-N PLL synthesizer covers all of the above listed frequency bands, using the same crystal for reference frequency generation.

The configurable digital modulator allows precise FSK modulation and Gaussian shaping (GFSK), which contributes to reduction of occupied bandwidth.

The output power of the integrated class-C RF power amplifier can be controlled over the SPI bus and if necessary, downsized (reduced) in digital steps.

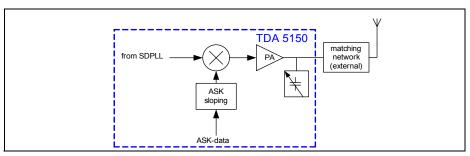

ASK shaping option contributes to reduced harmonics and minimized spectral splatter.

The data encoder supports NRZ, Manchester, Bi-Phase, and Miller encoding.

The device is fully configureable via the 3-wire Serial Peripheral Interface (SPI).

### 1.2 Features

- High resolution Sigma-Delta fractional-N PLL synthesizer (frequency step size down to 7 Hz)

- Multiband/Multichannel capability for the 300-320 MHz, 425-450 MHz and 863-928 MHz bands

- Modulation types ASK (OOK) with ASK shaping, FSK (CPFSK) and GFSK

- Multi-channel and channel hopping capability, 4 register banks for fast Tx frequency switching

- Configurable via 3-wire serial interface bus (SPI)

- · Manchester, Bi-Phase, and Miller encoding, on-chip PRBS9 scrambler

- Continuos checking of chip status by Fail-Safe mechanism

- Transparent and synchronized RF modulation mode

- Programmable clock divider output

- Configurable output power level from -10 dBm to +10 dbm, in 2 dB nominal steps

- Supply voltage range 1.9 V 3.6 V, 2 low battery detection thresholds, preset to 2.4V and 2.1V

- Low supply current (Sleep Mode < 0.8 μA, RF transmission 9 mA @ +5 dBm)</li>

- ESD protection up to +/- 4 kV on all pins

- Operating temperature range -40°C to +85°C

- Green Package TSSOP-10

# 1.3 Applications

- Short range wireless data transmission

- · Remote keyless entry transmitters

- Remote control units

- · Wireless alarm systems

- Remote metering

- Garage door openers

# 1.4 Order Information

| Туре     | Ordering Code | Package     |

|----------|---------------|-------------|

| TDA 5150 | SP000300415   | PG-TSSOP-10 |

### 1.5 Key Features overview

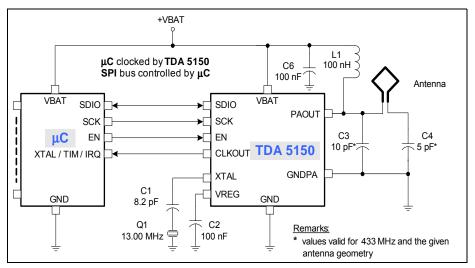

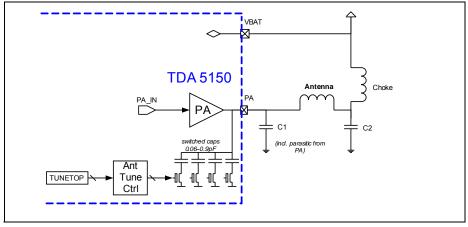

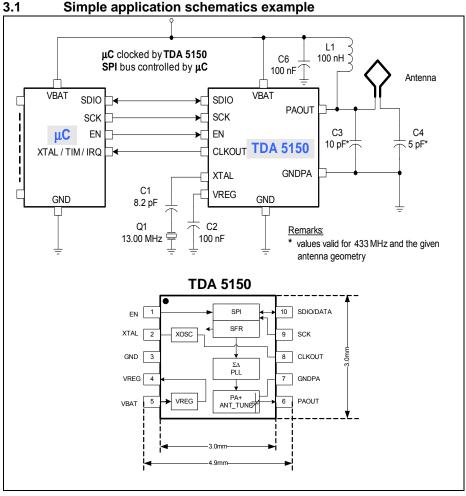

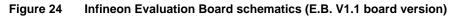

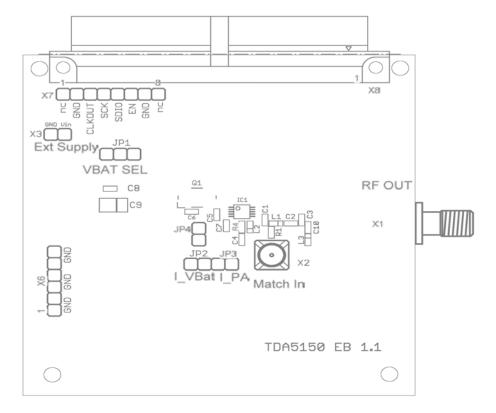

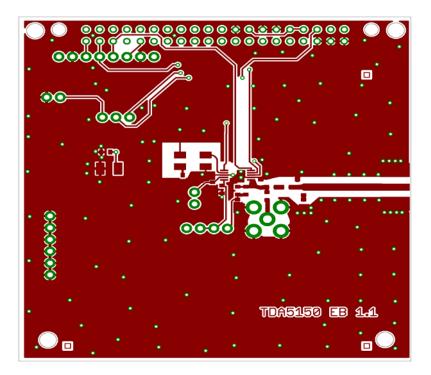

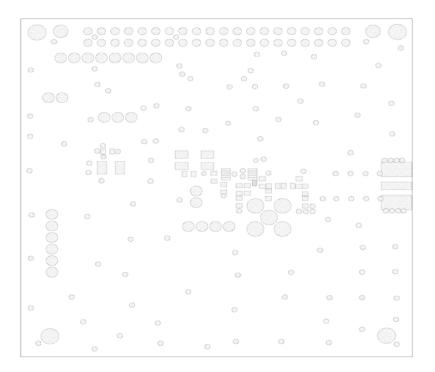

# 1.5.1 Typical Application Circuit

#### Figure 1 Minimum component count application circuit

The TDA 5150 application circuit shown demonstrates the ease and simplicity of an intelligent transmitter implementation. The  $\mu$ C configures the TDA5150 via 3-wire SPI, the SDIO line is used at the same time to transfer data on SPI bus and as digital data input into the RF modulator. The CLKOUT line may be used as clock source for the  $\mu$ C or as a timer for bitrate generation.

The matching shown is an example for a loop antenna application. Different antenna types (electrical monopole or dipole, magnetic loop etc.) as well as different layout versions might require component values which can differ from those given in above example. The antenna geometry has a major influence on the antenna impedance and consequently on the component values in the matching network.

# 1.5.2 Sigma-Delta fractional-N PLL with High Resolution

This type of PLL offers a multitude of advantages compared to fixed, integer division ratio PLLs.

In the reference oscillator circuit the same crystal can be used for all of the RF bands and frequencies (for example a 13 MHz crystal).

Dedicated crystals for each frequency are no longer required.

However by choice of crystal frequency a phenomenon, known as occurrence of fractional-N spurs must be kept in mind. The phenomenon and the countermeasures which should be taken to avoid it are described in detail in **Chapter 2.4.6.1**.

The PLL allows a direct (G)FSK modulation for reduced spurs and harmonics with high accuracy and resolution compared to legacy transmitters using crystal pulling for FSK modulation.

Synthesizer resolution down to 7 Hz for carrier frequency and FSK deviation allows fine tuning, correction of crystal tolerances and for temperature drift.

# 1.5.3 Reduction of Spurs and Occupied Bandwidth

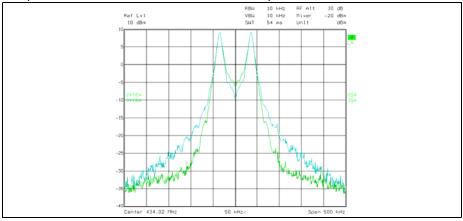

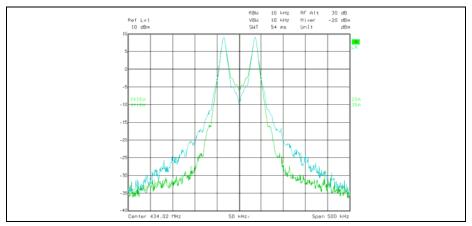

The direct FSK modulation and in addition the Gaussian FSK (GFSK) reduces spurs and occupied bandwidth. Bandwidth reduction is exemplified below

Figure 2 Spectrum of RF-signals with equal frequency deviations (± 35kHz), same 20kBit/s datarate and encoding (NRZ). Blue plot corresponds to FSK modulation and green to GFSK. Observe the difference in terms of occupied bandwidth between the signals.

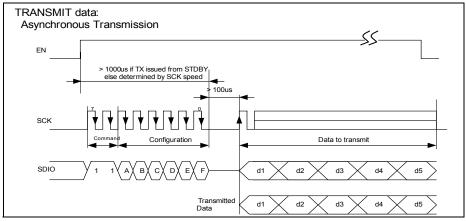

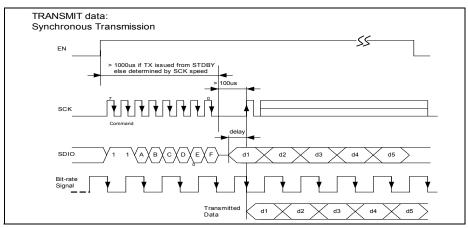

# 1.5.4 Asynchronous and Synchronous Transmission

TDA 5150 offers a simple asynchronous transmission mode (transparent modulation), whereby after the configuration word is downloaded into the transmitter's SFRs (via SPI bus) the data bitstream is output on the SDIO line and fed into the transmitter's RF modulator.

The CLKOUT signal can be used either as clock line for host  $\mu$ C or, alternatively, as timer base (flag) for bitrate generator (this last function should be implemented in  $\mu$ C).

In this mode, the bitrate is solely imposed and controlled by the  $\mu C$  software.

GFSK modulation and ASK shaping options are allowed in Asynchronous Mode.

In Synchronous Transmission Mode the bitrate is solely under the transmitter's control and fully timed by the TDA 5150. The CLKOUT is used to alert the  $\mu$ C about the request for next databit.

The  $\mu$ C may have a higher allowable processing delay tolerance, typically the duration of 1/2 bit, before sending the corresponding bit via SDIO line to transmitter.

Usage of data encoding option is allowed in Synchronous Mode.

# 1.5.5 Integrated Data Encoder

TDA 5150 comprises a Data Encoder which automatically generates encoded data from a regular (NRZ) bitstream. The supported data encoding modes are:

- Manchester code

- Differential Manchester code

- · Bi-phase space code

- · Bi-phase mark code

- Miller code (Delay modulation)

- NRZ

- Scrambling (PRBS9 generator)

All the encoded bitstreams can be level inverted (as part of the encoding option). The scrambling module (PRBS9 generator) is intended to be used for generation of pseudo-random data patterns (rather for Tx test scopes) or for basic level data encryption.

#### 1.5.6 Fail-Safe Mechanism

The Transmitter Status Register reports about failures such as: Brownout event, PLL lock error, VCO auto-calibration error and Register Parity error.

The Register Parity is a special safety feature. Each SFR (Special Function Register) has an extra parity bit which is automatically calculated and stored during a SFR write operation. During transmitter active state these parity bits, belonging to SFR content are continuously recalculated and compared against the stored values. Changes in the contents of writable SFRs without write command generate an SFR error event and an error flag is set.

To prevent erroneous transmissions (on wrong frequency or with erroneous modulation parameters, altered payload etc.) the activation of Fail-Safe mechanism is coupled with deactivation (switching off) of the RF Power Amplifier stages.

This additional feature inhibits the transmission if errors occur, thus preventing the transmission of erroneous datagrams or on false frequency

For details see the associated SFR description, and their interaction with the Fail-Safe Mechanism, as described in **Chapter 2.4.10**.

# 1.5.7 TESEUS - Configuration and Evaluation Tool

|                                          |                                                                       | A / Modulation   Transmission                                                                                     |                                                                              |

|------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Evaluation and System EmUlation Software | XTAL Settings<br>Xtal Freq. [MHz]: 13.000                             | CLKOUT Settings<br>CLKOUT<br>Disabled 0 — 1 Enabled<br>CLKOUT Selection:<br>Prescaler Counter<br>CLKOUT = XTAL/16 | TX Configuration Registers<br>Go2Sleep<br>Goto Standby                       |

| /stem EmU                                | Encoding Mode:<br>NRZ T<br>Data Inversion:                            | Calculator<br>Afterscaler CLK Div.<br>Prescaler CLK Div.                                                          | Off 0 J — 1 Standby<br>Power Down XOSC & Bypass<br>Enable 0 J — 1 Power Down |

| ion and S                                | Not Inverted 0 1 Inverted<br>PRBS Start Value: 0 •<br>Unscrambled 0 • | BDRDIV:<br>CLKOUT [kHz]: 812.500<br>Resulting Bitrate [kbps]: 3.149                                               | Failsafe Mechanism<br>On 0 J — 1 Off<br>Frequency Hopping                    |

| Evaluat                                  | Bit Count: 19                                                         | Resulting Chiprate [kbps]: 6.298                                                                                  | Enabled 0 — 1 Disabled                                                       |

| TDA5150 1                                |                                                                       | Voltage Supply<br>Voltage Regulator<br>Vreg [V]: 2.1 V                                                            | Vbat (from SIB) [V]: 3.0 +<br>SCK Frequency [kHz]: 50.0 +                    |

| SEUS -                                   |                                                                       | y Voltage Drop under 2.4V PLL Lock<br>y Voltage Drop under 2.1V Parity Err                                        | Read Status Registers                                                        |

|                                          | TDA5150 detected                                                      | ce Board connected                                                                                                | Update Registers                                                             |

#### Figure 3 TESEUS - First Tab of User Interface screen

TESEUS is a user-friendly, comfortable tool, suitable for generation of TDA 5150 configurations and testing them using a TDA 5150 Evaluation Board. Configurations can be automatically converted into register lists and implemented in C-code.

The pattern to be transmitted is written into a datagram- or TX file. A commented example TX file can be generated by TESEUS. This file might be edited using a standard text file editor, if changes of the transmit parameters and data patterns are required.

Note: for further details please consult the TESEUS User's Manual document.

# 2 TDA 5150 Functional Description

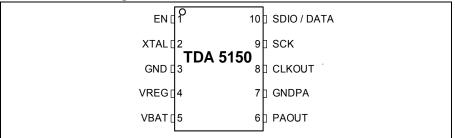

# 2.1 PIN Configuration, Pin-out

# 2.2 Pin Definition and Pin Functionality

| Pin<br>No. | Name | Pin<br>Type      | Equivalent I/O Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Function           |

|------------|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 1          | EN   | Digital<br>Input | VBat<br>VBat<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solution<br>Solu                                                                                                                                                                                                                                                                               | Enable 3-wire bus  |

| 2          | XTAL | Analog<br>Input  | VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VO.9Vdc<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VREG<br>VRE | Crystal Oscillator |

| Pin<br>No. | Name | Pin<br>Type      | Equivalent I/O Schematic  | Function                    |

|------------|------|------------------|---------------------------|-----------------------------|

| 3          | GND  | Supply           | GND GNDD GNDD GNDA GNDA O | Power supply<br>ground      |

| 4          | VREG | Analog<br>Output | VBAT                      | Voltage Regulator<br>output |

| 5          | VBAT | Supply           | VBAT                      | Power supply (+)            |

| Pin<br>No. | Name  | Pin<br>Type     | Equivalent I/O Schematic | Function                                     |

|------------|-------|-----------------|--------------------------|----------------------------------------------|

| 6          | PAOUT | RF-PA<br>Output | PAOUT                    | RF Power<br>Amplifier Output<br>(open drain) |

| 7          | GNDPA | Analog<br>GND   | GNDPA                    | RF Power<br>Amplifier<br>Ground return       |

| Pin<br>No. | Name   | Pin<br>Type       | Equivalent I/O Schematic | Function                      |

|------------|--------|-------------------|--------------------------|-------------------------------|

| 8          | CLKOUT | Digital<br>Output | CLKOUT                   | Programmable<br>Divided Clock |

| Pin<br>No. | Name | Pin<br>Type                 | Equivalent I/O Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Function         |

|------------|------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 9          | SCK  | Digital<br>Input            | SCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Clock 3-wire bus |

| 10         | SDIO | Digital<br>Input/<br>Output | SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_DATA<br>SDIO_SIN<br>SDIO_DATA<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO_SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN<br>SDIO<br>SIN | Data 3-wire bus  |

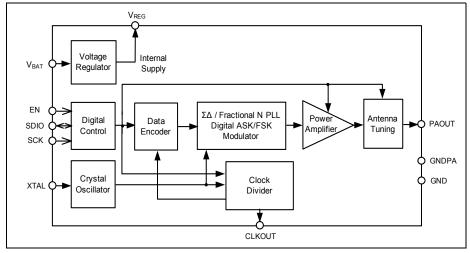

# 2.3 Functional Block Diagram

#### Figure 4 TDA 5150 Block Diagram

TDA 5150 is an SPI configurable fully integrated ASK/FSK/GFSK RF transmitter for the 300-320 MHz, 425-450 MHz and 863-928 MHz frequency bands. The input datastream, applied to the digital SDIO line is transposed and appears as modulated RF-signal, at the output of the integrated RF power amplifier. Signal encoding and spectrum is in accordance with the chosen modulation type (i.e ASK, FSK or GFSK) and encoding scheme.

TDA 5150 contains following major blocks which extend the functionality compared to legacy RF transmitters:

- An on-chip voltage regulator is delivering 2.1 V nominal supply voltage for the transmitter's functional units. In addition, the battery voltage is monitored and battery low and brown out flags are set, if a critical supply voltage drop event occurs.

- For avoidance of erroneous transmissions, the brownout flag is coupled with the RF Power Amplifier state control. If a brownout or critical voltage drop event occurs, the RF Power Amplifier is automatically switched off, as part of the Fail-Safe philosophy. The mechanism is explained in detail in Chapter 2.4.8.5

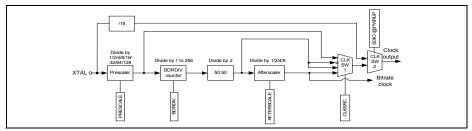

- The crystal oscillator and the associated clock divider(s) generate the required clock signals. There is an output line (CLKOUT) which may be used to clock a host μC, or for bit rate generation.

- A digital control logic, accessible for user via the SPI bus allows flexible and fast (re)configuration. At the same time it offers a simple but powerful Fail-Safe mechanism, which enhances the reliability of transmissions

- The data encoder synchronizes the bitstream to be transmitted with the internal bit clock. It supports different types of Manchester and Bi-Phase encodings and is able to generate PRBS9 pseudo-random patterns. The internal data encoder can be bypassed, allowing transmissions in direct (transparent) mode.

- The core element of the transmitter is the sigma-delta fractional-N PLL Synthesizer, used for carrier frequency control and as part of the digital modulator as well. It covers the frequency bands 300-320 MHz, 425-450 MHz and 863-928 MHz with outstanding frequency resolution. Only one, fixed frequency crystal (e.g. 13 MHz) is required for reference frequency generation. The synthesizer is characterized by short settling time. It is also used as direct FSK modulator, and together with a Gaussian filter, implemented by means of lookup table offers the functionality of a direct GFSK modulator.

- The integrated Power Amplifier is able to deliver up to +10dBm output power into a 50  $\Omega$  load (usually the antenna) via an external impedance matching network. In addition there are integrated capacitors, connected between GND and the RF-PA output, over SFR controlled on/off switches. These capacitors are elements of a software controlled antenna tuner. They may be used to fine-tune (adjust) the PA-output to Load matching network impedance, and thus to maintain good VSWR values over a wider frequency band. This is particularly useful if the transmitter is operated not only on a single frequency but in a given frequency band.

# 2.4 Functional Description

### 2.4.1 Special Function Registers

TDA 5150 is configurable by programming the Special Function Register bank (abbreviated SFRs) via the SPI interface.

Terminology and notations related to TDA5150 SFR set, list of symbols and programming restrictions are given in **Chapter 22 Register Terminology**.

Detailed description of SFR map, programming, usage and content explanations are found in the following chapters (§2.4.x.x and §2.5.x.x). See also Chapter 2.5.1 SFR Register List.

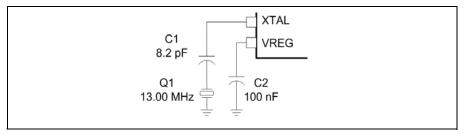

### 2.4.2 Power Supply Circuit

An internal **voltage regulator** generates a constant supply voltage (2.1V nominal) for most of the analog and digital blocks.

An external capacitor (100nF nominal value) connected between VREG (pin 4) and GND (pin 3) is necessary to guarantee stable functionality of the regulator.

The regulated voltage on VREG pin is not adjustable by user and it is not allowed to connect any additional, external loads to this pin, but the above mentioned decoupling capacitor.

In **STANDBY** state, a special, low-power voltage regulator is activated, which is supplying only the SPI bus interface, the SFR registers and the system controller.

In order to further reduce the current consumption, and keeping in mind that leakage currents can steeply increase by high temperatures, an additional low-power state, denoted **SLEEP** was defined. In this state most of the digital part is disconnected from the regulator (VREG). Only the SPI bus interface remains active. As a consequence, further power saving is achieved, but register content is lost by entering this mode.

See Chapter 2.4.9 Operating Modes for further informations.

#### 2.4.2.1 Brownout Detector

A Brownout Detector (abbreviated BOD) is integrated into the TDA 5150 transmitter.

Brownout is a condition where the supply voltage drops below a certain threshold level. By brownout events the integrity of SFRs can not be guaranteed, even if the dropout's duration is very short.

During active states, BOD monitors the VREG pin; during **STANDBY**, it monitors VBAT and VREG supply lines.

#### Table 1 BOD Thresholds

| Description                               |       | Monitored @ | min   | max   |

|-------------------------------------------|-------|-------------|-------|-------|

| Brownout Detection<br>Level—Active State  | VBDR  | VREG        | 1.7 V | 1.8 V |

| Brownout Detection<br>Level—StandBy State | VPDBR | VREG & VBAT | 0.7 V | 1.7 V |

If the BOD detects a brownout, the Power Amplifier is switched off and the SFRs are reset. The device is then forced to restart from the Power Up Reset condition. This ensures that the device is always in a well-defined logic state.

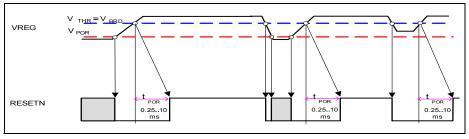

Figure 5 Power-on Reset/Brownout Detector

Brownout is indicated by bit BROUTERR (0x01.2) within SFR TXTSTAT (0x01).

**Note:** The BOD itself can not be used to guarantee the correct operation of analog sections, where the minimum operating voltage is defined to be 1.9 V; as this is larger than the maximum BOD voltage. In other words, in case of a supply voltage drop, the voltage region which is critical for reliable operation of the analog sections (min 1.9V) is reached before the brownout detector triggers (between 1.8..1.7V).

See also Chapter 4.2 for operating voltage limits.

# 2.4.2.2 Low Battery Detector

TDA 5150 has an embedded **Low Battery Detector** (**LBD**) block. In active modes, **LBD** monitors the voltage on VBAT supply line (pin 5). **LBD** has two activation thresholds, set to 2.4 V and 2.1 V. The status regarding supply voltage below threshold events can be updated by reading from SFR *TXSTAT*, bits 4 and 5 (0x01.5:4). These LBD flags are cleared after every transmission start. The LBD might be used as early warning for low battery voltage state (but before the battery voltage is dropping below the critical value, which renders normal operation capability).

# 2.4.2.3 SFRs related to Supply Voltage monitoring

| ADDR 0x01 |          | TXSTAT—Transmitter Status Register |                                                                         |                                                          |          |        |         |  |  |

|-----------|----------|------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------|----------|--------|---------|--|--|

|           |          |                                    |                                                                         |                                                          |          |        |         |  |  |

| Bit 7     | Bit 6    | Bit 5                              | Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         E |                                                          |          |        |         |  |  |

| 1         | n.u.     | LBD_2V1                            | LBD_2V4                                                                 | VAC_FAIL                                                 | BROUTERR | PARERR | PLLLDER |  |  |

| /         | 1        | r/0                                | r/0                                                                     | c/0                                                      | c/1      | c/0    | c/0     |  |  |

|           |          |                                    |                                                                         |                                                          |          |        |         |  |  |

| Bit 7     | 1        |                                    |                                                                         | Set to 1, ma                                             | ndatory  |        |         |  |  |

| Bit 5     | LBD_2V1  |                                    |                                                                         | battery low detected, threshold at 2.1 V -               |          |        |         |  |  |

| Bit 4     | LBD_2V4  |                                    |                                                                         | battery low detected, threshold at 2.4 V                 |          |        |         |  |  |

| Bit 3     | reserved |                                    |                                                                         | Don't care                                               |          |        |         |  |  |

| Bit 2     | BROUTE   | RR                                 |                                                                         | Brown out event                                          |          |        |         |  |  |

| Bit 1     | PARERR   |                                    |                                                                         | Parity error                                             |          |        |         |  |  |

| Bit 0     | PLLLDER  |                                    |                                                                         | PLL lock detector error                                  |          |        |         |  |  |

|           |          |                                    |                                                                         |                                                          |          |        |         |  |  |

| LBD_2V1   |          | Battery volta                      | ge drop belov                                                           | w 2.1 V detected if 1 - in standby mode, bit is invalid  |          |        |         |  |  |

| LBD_2V4   |          | Battery volta                      | ge drop belov                                                           | ow 2.4 V detected if 1 - in standby mode, bit is invalid |          |        |         |  |  |

| BROUTE    | RR       | Brownout ev                        | ent detected i                                                          | f <b>1</b>                                               |          |        |         |  |  |

| PARERR    |          | Parity error o                     | letected if 1                                                           |                                                          |          |        |         |  |  |

| PLLLDER   | R        | PLL lock erro                      | or detected if                                                          | 1                                                        |          |        |         |  |  |

# 2.4.3 Digital Control (3-wire SPI Bus)

The control interface is a 3-wire Serial Peripheral Interface (SPI), which is used for device control and data transmission.

# 2.4.3.1 SPI Pin Description

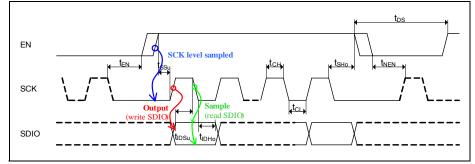

- **EN** enable input with embedded pull-down resistor. High level on EN input enables the SPI transmission. The rising edge of the EN signal triggers the selection of the active SCK edge (for the consequent data transfer, until the EN line goes again in low state) and transmission/ sampling of data between the device and the microcontroller can start. For details refer to Figure 6 and Figure 7.

- **SDIO 3-state input/output** This bidirectional line is used for data transfer between the TDA 5150 and external host (usually a  $\mu$ C). On-chip pull-down resistor is connected to this pin

SCK - clock input pin with embedded pull-down resistor. If SCK is at low level while EN goes high, the incoming SDIO data is sampled by falling edge of the SCK and the output SDIO data is set by the rising edge of SCK. Contrariwise, If SCK is at high level when EN goes high, the SDIO data is sampled with the rising edge of the SCK clock and output on SDIO by falling edge of the SCK clock. For details refer to Figure 6 and Figure 7.

SPI commands are started by the rising edge on the EN line and terminated by the falling edge on EN.

The available Burst Write mode allows configuration of several SFRs within one block access, without cycling the EN line Low - High - Low for each individual byte. By keeping the EN line at High level, subsequent bytes could be sent, and the byte address counter is autoincremented, thus speeding up the transfer on the SPI bus.

A self-explaining diagram is found here: Chapter 9 Timing Diagrams of 3-wire SPI.

The active edge of SCK (during SPI commands) is programmable, and it is determined by the level on SCK line at the moment of activation of the EN line (rising edge on EN).

If SCK is low at that moment, the incoming SDIO data will be sampled with the falling edge of SCK, and output by rising edge of SCK (see **Figure 6** below)..

#### Figure 6 SPI Timing — SCK low at rising edge of EN

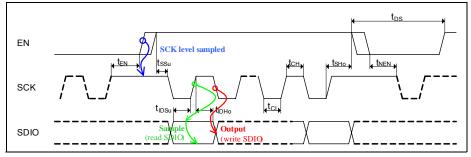

If SCK is high during occurrence of rising edge on EN, incoming SDIO data is sampled with the rising edge on SCK, and output by falling edge of SCK, as illustrated in **Figure 7**.

Figure 7 SPI Timing — SCK high at rising edge of EN

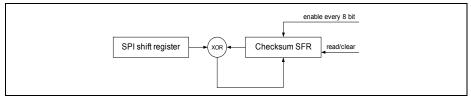

# 2.4.3.2 SPI XOR Checksum

The SPI block includes a safety feature for checksum calculation. This is achieved by means of XOR operation between the address and the data during write operation of SFR registers. The checksum is in fact the XOR of the data 8-bitwise after every 8 bits of the SPI write command. The calculated checksum value is then automatically written into SFR *SPICHKSUM* (0x00) and can be compared with the expected value.By executing a read operation of SFR *SPICHKSUM* (0x00) the register content is automatically cleared (after read). Read access to any of the other readable SFRs does not influence the SFR *SPICHKSUM*.

#### Figure 8 Generating the Checksum of SFRs, block diagram

Example:

Write to SFR address 0x04, data 0x02, address 0x05, data 0x01

| Bytes transmitted via SPI | Result in Checksum Register |

|---------------------------|-----------------------------|

| 0000 0100                 | 0000 0100                   |

| 0000 0010                 | 0000 0110                   |

| 0000 0101                 | 0000 0011                   |

| 0000 0001                 | 0000 0010                   |

After writing into the registers, content of checksum SFR SPICHKSUM (0x00) will be 0x02.

### 2.4.3.3 Command Byte Structure

First byte of each SPI sequence is the Command Byte, with the following structure:

| Functio | on Code | Command Byte Configuration |                   |  |  |  |  |  |

|---------|---------|----------------------------|-------------------|--|--|--|--|--|

| C1      | C0      | Address                    |                   |  |  |  |  |  |

| х       | x       | A5                         | A5 A4 A3 A2 A1 A0 |  |  |  |  |  |

The first 2 bits **C1**, **C0** of the Command Byte are the function code field.

They define the command to be performed, according to the following table:

| C1 | C0 | Function Code Configuration Bits                                                                                                                                |

|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | Write data into SFR register<br><a5:a0> field contains the SFR register's address</a5:a0>                                                                       |

|    |    | There are 2 possible write modes (controlled by state of EN line):<br>1. write to a single address                                                              |

|    |    | 2. burst mode write (with address auto increment)                                                                                                               |

| 0  | 1  | Read data from SFR, <a5:a0> points to register address</a5:a0>                                                                                                  |

| 1  | 0  | Reserved (do not use)                                                                                                                                           |

| 1  | 1  | Transmit Command Byte<br>Bits <a5:a0>within this byte define the transmission parameters<br/>(see Chapter 2.4.3.4 Transmit Command for command fields).</a5:a0> |

The **Write / Read Command** bytes are used for device control. Bit fields <A5:A0> within **Command Byte** are used to specify the addressed SFR register.An overview and register map is given in **Chapter 2.5.1 SFR Register List**.

There are two ways to program the SFR registers:

- 1. by sending a Write command individually, for each register which should be written.

- 2. by sending a Burst Write command, which allows sequential programming.

# Attention: Writing to address space beyond the valid SFR address range [0x04 - 0x27] is prohibited, and may lead to system malfunction.

### 2.4.3.4 Transmit Command

The **Transmit Command Byte** is used for **data transmission**. It precedes the datagram to be transmitted. The Transmit Command Byte format is described in the following table:

| C1 | C0 |             | Transmi                   | t Command Configuration                                                                                                                                                                                                                                                                          |  |  |

|----|----|-------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    |    | Bit         | Function                  | Value, description                                                                                                                                                                                                                                                                               |  |  |

| 1  | 1  | A           | Data sync                 | 0: off<br>1: on (at the same time Bit C - Encoding<br>must be set also to 1>int. Encoding)                                                                                                                                                                                                       |  |  |

| 1  | 1  | В           | PA mode                   | 0: PA off at the falling edge of EN<br>(synchronized with bit-rate if bit A is hig<br>1: SDIO/DATA is latched at the falling<br>edge of EN, PA stays on, TX data are ke<br>constant. After the time-out of 65536 / $f_s$<br>which is ~5 ms for a 13 MHz crystal, PA<br>and PLL are switched off. |  |  |

| 1  | 1  | С           | Encoding                  | 0: off<br>1: on (selects SFR register for encoding<br>Bit A must be also set to1>Data sync)                                                                                                                                                                                                      |  |  |

| 1  | 1  | D           | Pwr. level/<br>ModSetting | 0: selects PowerLevel/Modulation Setting1<br>1: selects Power Level/Modulation Setting2                                                                                                                                                                                                          |  |  |

| 1  | 1  | <e,f></e,f> | Frequency<br>selection    | 0 (00): selects frequency channel A<br>1 (01): selects frequency channel B<br>2 (10): selects frequency channel C<br>3 (11): selects frequency channel D<br>(for description of frequency channels<br>AD programming see<br>Chapter 2.4.11.3 Channel Hopping)                                    |  |  |

Note: After the last configuration bit for a new transmission was sent, a break of at least 100  $\mu$ s must be provided in order to achieve PLL settling and lock on the selected channel frequency.

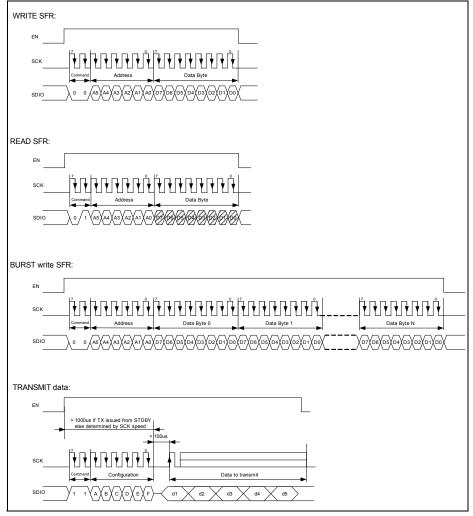

# 2.4.3.5 Timing Diagrams

In the following timing diagrams the 4 possible SPI commands are shown. The examples are valid for the case of SCK is low when EN line goes from Low into High (rising edge).

Therefore the incoming SDIO data is sampled at the falling edge of SCK, and data is output on SDIO line by the rising edge of SCK signal.

Figure 9 Timing Diagrams of 3-wire SPI

Note: In order to minimize cross-talk between SDIO and SCK lines, it is recommended to keep the SCK either Low or High, but avoid transitions during RF transmission.

Previous Chapter 2.4.3.4 Transmit Command gives an in-depth overview of Transmit Command structure.

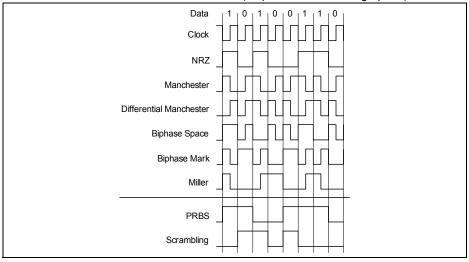

# 2.4.4 Data Encoder

The Data Encoder is used in the so-called Synchronous Transmission Mode.

A description of this transmission mode is found in **Chapter 2.4.11.2 Synchronous Transmission**.

In Synchronous Transmission Mode the Encoder has to be used. If no specific encoding of SDIO data shall be done, select NRZ as encoding scheme.

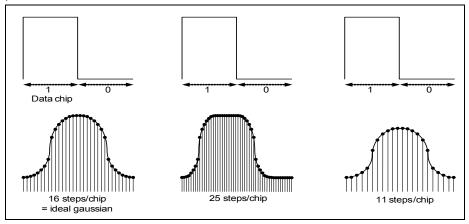

**Definition**: 'bit-rate' is the number of transmitted bits per second and expressed in [bits/sec]. Besides NRZ all the other implemented encoding methods split a single bit into two elementary parts, the so-called chips. Therefore we also talk about a chip-rate, which is an "n" multiple of the data-rate.

For NRZ (which means no extra encoding) n = 1 (data-rate = chip-rate), and for all other implemented encoding methods n = 2, or the chip-rate is twice the bit-rate.

The TDA 5150 supports the following encoding types:

- Manchester code

- Differential Manchester code

- Bi-phase space code

- · Bi-phase mark code

- Miller code (Delay modulation)

- NRZ

- Scrambling (PRBS9 generator)

All encoded bitstreams can be level inverted (as part of the encoding option)

#### Figure 10 Coding Schemes

The Data Encoder option is enabled by bit C of Transmit Command (Data Encoder enabled if bit C=1). See also **Chapter 2.4.3.4 Transmit Command** for command structure. If the Data Encoder is enabled, bit A must to be set for Synchronous Transmission Mode as well (Bit A=1 and Bit C=1, this last to enable encoding).

The selection of encoding mode is done via bits ENCODE (0x05.2:0) of SFR *TXCFG1*. (0x05). At the same time bit INVERT (0x05.3) of the same SFR enables the inversion of an already encoded bit stream.

The encoding activation entry point can be configured in SFR ENCCNT (0x27).

By initializing the SFR *ENCCNT* (0x27) with 0x00, already the first bit is encoded. If for example ENCCNT = 0x10, the first 16 bits should remain unencoded. This method allows to keep the first N bits unencoded within a datagram (in fact plain NRZ), followed by encoded bits (of the same datagram).The encoding scheme is selected by bit-field ENCMODE (0x05.2:0) of SFR *TXCFG1*.

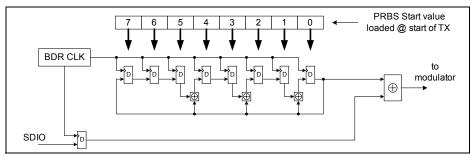

# 2.4.4.1 PRBS9 Generator, Data Scrambler

TDA 5150 contains a PRBS9 generator, suitable for generation of pseudo-random NRZ data patterns. The PRBS9 datastream satisfies (in general lines) the requirements for random distribution (even if longer PRBS polynomials come closer to "true" random distribution) and therefore it can be useful for Transmitter RF tests, for instance by measurement of the "Occupied RF Bandwidth".

In addition the generated PRBS9 pattern can be XOR'ed with a real data pattern sent by the microcontroller and this way "scramble" this data pattern.

# Attention: The data scrambling functionality is intended to enhance the clock recovery performance of the Receiver Station. It is not suitable, as stand-alone encryption method for security applications!

PRBS9 is a well known standard in the class of pseudo-random patterns, and is implemented within the TDA 5150 by a subpart with following block diagram:

Figure 11 PRBS9 Generator and Data Scrambler

The feedback branches within the PRBS9 generator are fixed (as shown above), but the PRBS generation can be influenced by SFR configuration in the following manner:

- A start value for the PRBS9 Generator can be programmed in SFR PRBS Start Value (0x08). The reset value is 0xAB (10101011). Choice of 0x00 as start value is not allowed, because the output of PRBS9 Generator should "lock" and will never go in High. The PRBS Start Value is loaded into the PRBS9 Generator at the start of each transmission.

- If the Data Scrambler is used, the start of scrambling can be configured in SFR ENCCNT (0x27). If ENCCNT is 0, already the first bit is XOR'ed with PRBS9. If for example ENCCNT = 0x10, the first 16 bits stay unscrambled. This is necessary if a data frame should have always the same wake up and synchronization part, but the payload should be pseudo-random for sensitivity measurements or to enhance the clock recovery on the receiver side.

# 2.4.4.2 SFRs related to Transmitter Configuration and Data Encoding

| ADDR 0x05        |         | TXCFG1—Transmitter Configuration Register 1 |                                 |                                   |                               |                  |         |  |  |

|------------------|---------|---------------------------------------------|---------------------------------|-----------------------------------|-------------------------------|------------------|---------|--|--|

|                  |         |                                             |                                 |                                   |                               |                  |         |  |  |

| Bit 7            | Bit 6   | Bit 5                                       | Bit 4                           | Bit 3                             | Bit 2                         | Bit 1            | Bit 0   |  |  |

| GO2SLEEP         | ASKFSK2 | ASKFSK1                                     | ASKSLOPE                        | INVERT                            | ENCMODE                       | ENCMODE          | ENCMODE |  |  |

| cw/0             | w/0     | w/1                                         | w/0                             | w/0                               | w/1                           | w/0              | w/1     |  |  |

|                  | 1       |                                             |                                 |                                   |                               |                  |         |  |  |

| Bit 3            | INVERT  |                                             |                                 | Data inversion                    |                               |                  |         |  |  |

| Bit <2:0>        | ENCMOD  | Ε                                           |                                 | Encoding mode bit <2:0>           |                               |                  |         |  |  |

|                  | 1       |                                             | 1                               | 1                                 |                               |                  |         |  |  |

| INVERT           |         | Encoded dat                                 | a inversion er                  | nable                             |                               |                  |         |  |  |

|                  |         | 0: data not ir                              | data not inverted               |                                   |                               | 1: data inverted |         |  |  |

| ENCMOD           | E       | Encoding mo                                 | mode, code selection (3 bits)   |                                   |                               |                  |         |  |  |

| 000:<br>Manchest |         | 000:<br>Manchester                          | 010:<br>Biphase<br>Space        | <b>100</b> :<br>Miller<br>(Delay) | 110:<br>Scrambling<br>(PRBS)  |                  |         |  |  |

|                  |         | <b>001</b> :<br>Differential<br>Manchester  | <b>011</b> :<br>Biphase<br>Mark | 101:<br>NRZ                       | 111:<br>not used<br>(data =0) |                  |         |  |  |

| ADDR 0x08                                                                                                                |       | PRBS—PRBS Start Value |       |                            |       |       |                |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|-------|----------------------------|-------|-------|----------------|--|--|

|                                                                                                                          |       |                       |       |                            |       |       |                |  |  |

| Bit 7                                                                                                                    | Bit 6 | Bit 5                 | Bit 4 | Bit 3                      | Bit 2 | Bit 1 | Bit 0          |  |  |

| PRBS                                                                                                                     | PRBS  | PRBS                  | PRBS  | PRBS                       | PRBS  | PRBS  | PRBS           |  |  |

| w/1                                                                                                                      | w/0   | w/1                   | w/0   | w/1                        | w/0   | w/1   | w/1            |  |  |

|                                                                                                                          |       |                       |       |                            |       |       |                |  |  |

| Bit <7:0>                                                                                                                | PRBS  |                       |       | PRBS start value bit <7:0> |       |       |                |  |  |

|                                                                                                                          | 1     |                       | L.    |                            |       |       |                |  |  |

| PRBS PRBS start value (8 bits), the PRBS generator uses this value as a starting value after each transmission beginning |       |                       |       |                            |       |       | starting value |  |  |

| ADDR 0x27                                                                                                                                                                                                                                                          |        | ENCCNT - Encoding start bit counter |        |                                      |        |        |                        |  |  |  |