### Freescale Semiconductor Advance Information

# **Dual High-speed CAN Transceiver**

The CM0902 is a SMARTMOS dual high-speed (up to 1 Mbit/s) CAN transceiver device, providing the physical interface between the CAN protocol controller of an MCU and the physical dual wire CAN bus. Both channels are completely independent, featuring CAN bus wake-up on each CAN interface, and TXD dominant timeout functionality (33CM0902 only).

The CM0902 is packaged in a 14-pin SOIC, with industry standard pin out, and offers excellent EMC and ESD performance without the need for external filter components. The CM0902 comes in two variants: 33CM0902 and 34CM0902 for Automotive and Industrial applications respectively.

### Features

- · Very low-current consumption in standby mode

- Compatible with +3.3 V or +5.0 V MCU interface

- Standby mode with remote CAN wake-up

- Pin and function compatible with market standard

Cost efficient robustness:

- · High system level ESD performance

- Very high electromagnetic immunity and low electromagnetic emission without common mode choke or other external components.

### Fail-safe behaviors:

- TXD Dominant timeout (33CM0902 only)

- Ideal passive behavior when unpowered, CAN bus leakage current  ${<}10~\mu\text{A}.$

- V<sub>DD</sub> and V<sub>IO</sub> monitoring

### CAN HIGH-SPEED TRANSCEIVER

### Automotive Applications (33CM0902)

- Supports automotive CAN high-speed applications

- Body electronics

- Power train

- Chassis and safety

- Infotainment

- · Diagnostic equipment

- Accessories

### Industrial Applications (34CM0902)

- Transportation

- Backplanes

- Lift/elevators

- Factory automation

- · Industrial process control

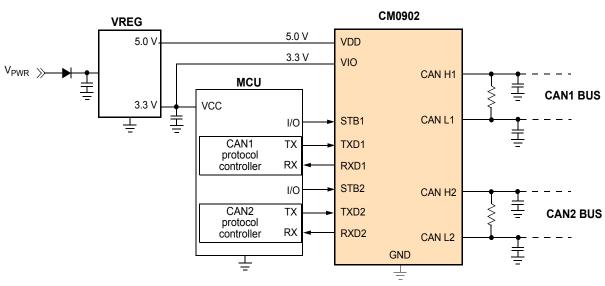

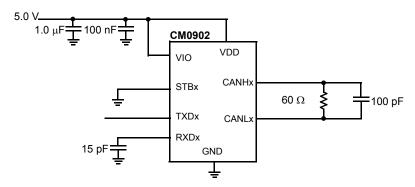

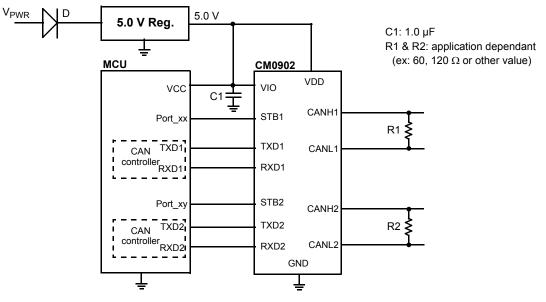

Figure 1. Simplified Application Diagram

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice. © Freescale Semiconductor, Inc., 2015. All rights reserved.

# **Table of Contents**

| 1 | Orderable Parts                                               | 3  |

|---|---------------------------------------------------------------|----|

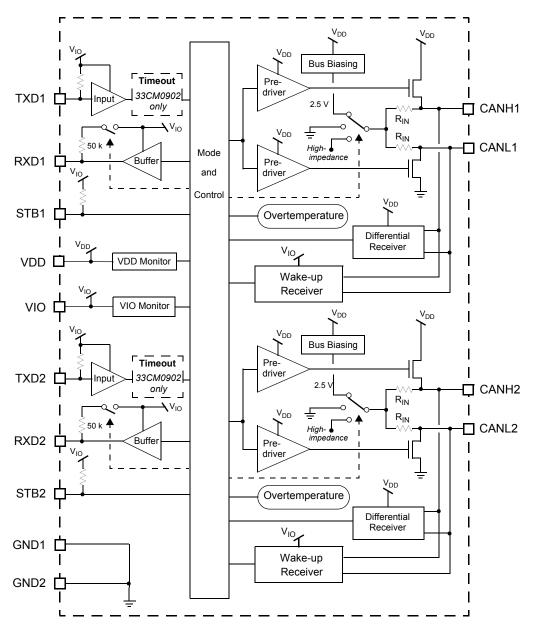

| 2 | Internal Block Diagram                                        | 4  |

| 3 | Pin Connections                                               | 5  |

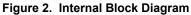

|   | 3.1 Pinout                                                    | 5  |

|   | 3.2 Pin Definitions                                           | 5  |

| 4 | General Product Characteristics                               | 6  |

|   | 4.1 Maximum Ratings                                           | 6  |

|   | 4.2 Thermal Characteristics                                   | 7  |

|   | 4.3 Electrical Characteristics                                | 8  |

|   | 4.4 Operating Conditions                                      | 14 |

| 5 | General IC Functional Description and Application Information | 15 |

|   | 5.1 Features                                                  | 15 |

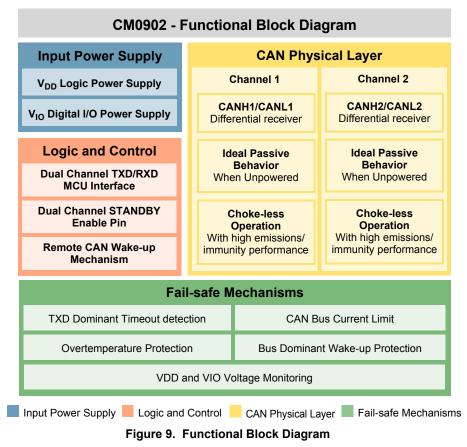

|   | 5.2 Functional Block Diagram                                  | 16 |

|   | 5.3 Functional Description                                    | 16 |

| 6 | Functional Operation                                          | 18 |

|   | 6.1 Operating Modes                                           | 18 |

|   | 6.2 Fail-safe Mechanisms                                      | 18 |

|   | 6.3 Device Operation Summary                                  | 20 |

| 7 | Typical Applications                                          | 21 |

|   | 7.1 Application Diagrams                                      | 21 |

| 8 | Packaging                                                     | 23 |

|   | 8.1 Package Mechanical Dimensions                             | 23 |

| 9 | Revision History                                              | 25 |

|   |                                                               |    |

# 1 Orderable Parts

This section describes the part numbers available to be purchased along with their differences.

#### Table 1. Orderable Part Variations

| Part Number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package      | TXD dominant protection |

|----------------------------|-------------------------------|--------------|-------------------------|

| MC33CM0902WEF              | -40 °C to 125 °C              | SOIC 14 pins | Available               |

| MC34CM0902WEF              | -40 °C to 85 °C               |              | Not Available           |

Notes

1. To Order parts in Tape & Reel, add the R2 suffix to the part number.

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to http://www.freescale.com and perform a part number search.

# 2 Internal Block Diagram

# 3 Pin Connections

## 3.1 Pinout

Figure 1. 14-Pin SOIC Pinout

# 3.2 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 15.

### Table 2. CM0902 Pin Definitions

| Pin Number | Pin Name | Pin Function | Definition                                     |

|------------|----------|--------------|------------------------------------------------|

| 1          | TXD1     | Input        | CAN1 bus transmit data pin                     |

| 2          | GND1     | Ground       | Ground 1                                       |

| 3          | VDD      | Input        | 5.0 V input supply for CAN driver and receiver |

| 4          | RXD1     | Output       | CAN1 bus receive data pin                      |

| 5          | GND2     | Ground       | Ground 2                                       |

| 6          | TXD2     | Input        | CAN2 bus transmit data pin                     |

| 7          | RXD2     | Output       | CAN2 bus receive data pin                      |

| 8          | STB2     | Input        | Standby input for CAN2 mode selection          |

| 9          | CANL2    | Input/Output | CAN2 low pin                                   |

| 10         | CANH2    | Input/Output | CAN2 high pin                                  |

| 11         | VIO      | Input        | Input supply for the digital input output pins |

| 12         | CAN L1   | Input/Output | CAN1 low pin                                   |

| 13         | CAN H1   | Input/Output | CAN1 high pin                                  |

| 14         | STB1     | Input        | Standby input for CAN1 mode selection          |

# 4 General Product Characteristics

## 4.1 Maximum Ratings

### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                   | Description (Rating)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Min. | Max.                                                          | Unit | Notes |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------|------|-------|

|                                          | ATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 1 1                                                           |      |       |

| V <sub>DD</sub>                          | V <sub>DD</sub> Logic Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | 7.0                                                           | V    |       |

| V <sub>IO</sub>                          | Input/Output Logic Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 7.0                                                           | V    |       |

| V <sub>STB1</sub><br>V <sub>STB2</sub>   | Standby pin Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 7.0                                                           | V    |       |

| V <sub>TXD1</sub><br>V <sub>TXD2</sub>   | TXD Maximum Voltage Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 7.0                                                           | V    |       |

| V <sub>RXD1</sub><br>V <sub>RXD2</sub>   | RXD Maximum Voltage Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 7.0                                                           | V    |       |

| V <sub>CANH1</sub><br>V <sub>CANH2</sub> | CANH Bus Pin Maximum Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -40  | 40                                                            | V    |       |

| V <sub>CANL1</sub><br>V <sub>CANL2</sub> | CANL Bus Pin Maximum Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -40  | 40                                                            | V    |       |

| V <sub>ESD</sub>                         | <ul> <li>ESD Voltage</li> <li>Human Body Model (HBM) (all pins except CANHx and CANLx pins)</li> <li>Human Body Model (HBM) (CANHx, CANLx pins)</li> <li>Machine Model (MM)</li> <li>Charge Device Model (CDM) (corner pins)</li> <li>System level ESD <ul> <li>330 Ω / 150 pF unpowered according to IEC61000-4-2:</li> <li>330 Ω / 150 pF unpowered according to OEM LIN, CAN, FLexray Conformance</li> <li>2.0 kΩ / 150 pF unpowered according to ISO10605.2008</li> <li>2.0 kΩ / 330 pF powered according to ISO10605.2008</li> </ul> </li> </ul> |      | ±2000<br>±8000<br>±200<br>±500(±750)<br>10<br>10<br>10<br>8.0 | V    | (2)   |

Notes

2. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), the Machine Model (MM) ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ), and the Charge Device Model.

# 4.2 Thermal Characteristics

### Table 4. Thermal Ratings

| Symbol                           | Description (Rating)                                                | Min.       | Тур. | Max.       | Unit | Notes |

|----------------------------------|---------------------------------------------------------------------|------------|------|------------|------|-------|

| ERMAL RATI                       | NGS                                                                 |            | •    | •          |      |       |

| T <sub>A</sub><br>T <sub>J</sub> | Operating Temperature <ul> <li>Ambient</li> <li>Junction</li> </ul> | -40<br>-40 |      | 125<br>150 | °C   |       |

| T <sub>STG</sub>                 | Storage Temperature                                                 | -55        |      | 150        | °C   |       |

| T <sub>PPRT</sub>                | Peak Package Reflow Temperature During Reflow                       | -          |      | _          | °C   |       |

|                                  | STANCE AND PACKAGE DISSIPATION RATINGS                              |            |      |            |      |       |

| $R_{\theta J A}$                 | Junction-to-Ambient, Natural Convection, Single-layer Board         | -          |      | 140        | °C/W |       |

| T <sub>SD</sub>                  | Thermal Shutdown                                                    |            | 185  | _          | °C   |       |

| T <sub>SDH</sub>                 | Thermal Shutdown Hysteresis                                         | -          | 10   |            | °C   |       |

#### **Electrical Characteristics** 4.3

#### **Static Electrical Characteristics** 4.3.1

### Table 5. Static Electrical Characteristics

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, 2.8 V  $\leq$  V<sub>IO</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0.0 V, R on CANx bus (R<sub>L</sub>) = 60  $\Omega$ , unless otherwise noted. Typical values noted reflect the approximate parameter at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol             | Characteristic                                                                                                                                                                                                                                     | Min.        | Тур.         | Max.             | Unit           | Notes |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|------------------|----------------|-------|

|                    | /DD                                                                                                                                                                                                                                                | L           |              | L                | 1              |       |

| V <sub>DD</sub>    | VDD Supply Voltage Range <ul> <li>Nominal operation</li> </ul>                                                                                                                                                                                     | 4.5         | _            | 5.5              | V              |       |

| V <sub>DD_UV</sub> | VDD Undervoltage Threshold                                                                                                                                                                                                                         |             | -            | 4.5              | V              |       |

| I <sub>VDD</sub>   | <ul> <li>VDD Supply Current</li> <li>Normal mode, TXD1 and TXD2 High</li> <li>Normal mode, TXD1 and TXD2 Low</li> <li>Standby mode</li> </ul>                                                                                                      | -<br>-<br>- | -<br>80<br>- | 8.0<br>130<br>10 | mA<br>mA<br>μA | (3)   |

|                    | /IO                                                                                                                                                                                                                                                |             |              |                  |                |       |

| V <sub>IO</sub>    | VIO Supply Voltage Range <ul> <li>Nominal operation</li> </ul>                                                                                                                                                                                     | 2.8         | _            | 5.5              | V              |       |

| V <sub>IO_UV</sub> | VIO Undervoltage threshold                                                                                                                                                                                                                         | -           | -            | 2.8              | V              |       |

| I <sub>VIO</sub>   | <ul> <li>VIO Supply Current</li> <li>Normal Mode (TXD1/TXD2 high CAN1/2 bus in recessive state)</li> <li>Normal Mode (TXD1, TXD2 high, CAN1/2 bus in dominant state)</li> <li>Standby mode (STB1 and STB2 high, BUS in recessive state,</li> </ul> | -<br>-<br>- | -<br>-<br>5  | 400<br>2.0<br>20 | μA<br>mA<br>μA |       |

Notes

3.  $I_{VDD}$  for CAN1 or CAN2 operation

wake-up filter and wake-up time out not active)

wake- up filter and wake-up time out active)

· Standby mode (STB1 and STB2 high, BUS in recessive state,

#### **STB1 INPUT**

| V <sub>STB1</sub>    | Input Voltages <ul> <li>High level input voltage</li> <li>Low level input voltage</li> <li>Input threshold hysteresis</li> </ul> | 0.7 x V <sub>IO</sub><br>-<br>200 |     | _<br>0.3<br>_ | V<br>V<br>mV |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----|---------------|--------------|--|

| R <sub>PU-STB1</sub> | Pull-up resistor to V <sub>IO</sub>                                                                                              | -                                 | 100 | -             | kΩ           |  |

| V <sub>TXD1</sub>    | Input Voltages <ul> <li>High level input voltage</li> <li>Low level input voltage</li> <li>Input threshold hysteresis</li> </ul> | 0.7 x V <sub>IO</sub><br>-<br>200 | -<br>-<br>300 | _<br>0.3<br>_ | V<br>V<br>mV |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------|---------------|--------------|--|

| R <sub>PU-TXD1</sub> | Pull-up Resistor to V <sub>IO</sub>                                                                                              | 5.0                               | -             | 50            | kΩ           |  |

**RXD1 OUTPUT**

|   | I <sub>RXD1</sub>    | Output Current<br>• RXD1 high, VRXD1 high = V <sub>IO</sub> - 0.4 V<br>• RXD1 low, VRXD1 high = 0.4 V | -5.0<br>1.0 | -2.5<br>2.5 | -1.0<br>5.0 | mA |  |

|---|----------------------|-------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|----|--|

| F | R <sub>PU-RXD1</sub> | Pull-up Resistor to $V_{\text{IO}}$ (in Standby mode, without toggling - no wake-up report)           | 25          | 50          | 90          | kΩ |  |

300

μA

### Table 5. Static Electrical Characteristics (continued)

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, 2.8 V  $\leq$  V<sub>IO</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0.0 V, R on CANx bus (R<sub>L</sub>) = 60  $\Omega$ , unless otherwise noted. Typical values noted reflect the approximate parameter at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                   | Characteristic                                                                                                                                                                                                                                                                           | Min.         | Тур.       | Max.        | Unit            | Notes |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|-------------|-----------------|-------|

| CANL1 and CAN            | H1 Pins                                                                                                                                                                                                                                                                                  |              | 1          | 1           | 1               |       |

| V <sub>REC1</sub>        | Recessive Voltage, TXD1 high, no load<br>• CANL1 recessive voltage<br>• CANH1 recessive voltage                                                                                                                                                                                          | 2.0<br>2.0   | 2.5<br>2.5 | 3.0<br>3.0  | V               |       |

| V <sub>DIFF_REC1</sub>   | CANH1 - CANL1 Differential Recessive Voltage, TXD1 high, no load                                                                                                                                                                                                                         | -50          | -          | 50          | mV              |       |

| V <sub>REC_SM1</sub>     | Recessive voltage, sleep mode, no load<br>• CANL1 recessive voltage<br>• CANH1 recessive voltage                                                                                                                                                                                         | -0.1<br>-0.1 | _          | 0.1<br>0.1  | v               |       |

| V <sub>DOM1</sub>        | Dominant Voltage, TXD1 low (t < TX <sub>DOM</sub> ), R <sub>L</sub> = 45 to 65 Ω<br>• CANL1 dominant voltage<br>• CANH1 dominant voltage                                                                                                                                                 | 0.5<br>2.75  |            | 2.25<br>4.5 | v               |       |

| V <sub>DIFF_DOM1</sub>   | CANH1 - CANL1 Differential Dominant Voltage, R <sub>L</sub> = 45 to 65 $\Omega$ , TxD1 <sub>LOW</sub>                                                                                                                                                                                    | 1.5          | 2.0        | 3.0         | V               |       |

| V <sub>SYM1</sub>        | Driver symmetry CANH1 + CANL1                                                                                                                                                                                                                                                            | 0.9          | 1.0        | 1.1         | V <sub>DD</sub> |       |

| I <sub>LIM1</sub>        | Current limitation, TXD1 low (t < TX <sub>DOM</sub> )<br>• CANL1 current limitation, CANL1 5.0 V to 28 V<br>• CANH1 current limitation, CANH1 = 0 V                                                                                                                                      | 40<br>-100   |            | 100<br>-40  | mA              |       |

| V <sub>DIFF_THR1</sub>   | CANH1 - CANL1 Differential Input Threshold                                                                                                                                                                                                                                               | 0.5          | -          | 0.9         | V               |       |

| V <sub>DIFF_HYS1</sub>   | CANH1 - CANL1 Differential Input Voltage Hysteresis                                                                                                                                                                                                                                      | 50           | -          | 400         | mV              |       |

| V <sub>DIFF_THR_S1</sub> | CANH1 - CANL1 Differential Input Threshold, in Standby mode                                                                                                                                                                                                                              | 0.4          | -          | 1.15        | V               |       |

| V <sub>CM1</sub>         | Common Mode Voltage                                                                                                                                                                                                                                                                      | -15          | -          | 20          | V               |       |

| R <sub>IN1</sub>         | Input Resistance<br>• CANL1 input resistance<br>• CANH1 input resistance                                                                                                                                                                                                                 | 5.0<br>5.0   |            | 50<br>50    | kΩ              |       |

| R <sub>IN_DIFF1</sub>    | CANH1, CANL1 Differential Input Resistance                                                                                                                                                                                                                                               | 10           | -          | 100         | kΩ              |       |

| R <sub>IN_MATCH1</sub>   | Input Resistance Matching                                                                                                                                                                                                                                                                | -3.0         | -          | 3.0         | %               |       |

| I <sub>IN_UPWR1</sub>    | $ \begin{array}{l} \mbox{CANL1 or CANH1 input current, device unpowered, VDD = VIO = 0 V, \\ \mbox{VCANL1 and VCANH1 0.0 to 5.0 V range} \\ \mbox{ · VDD connected with R=0.0 K}_{\Omega} \mbox{ to GND} \\ \mbox{ · VDD connected with R=47 K}_{\Omega} \mbox{ to GND} \\ \end{array} $ | -10<br>-10   | _          | 10<br>10    | μΑ              |       |

### Table 5. Static Electrical Characteristics (continued)

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, 2.8 V  $\leq$  V<sub>IO</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0.0 V, R on CANx bus (R<sub>L</sub>) = 60  $\Omega$ , unless otherwise noted. Typical values noted reflect the approximate parameter at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                 | Characteristic                                                                                                                                                         | Min.                              | Тур.          | Max.          | Unit            | Notes |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------|---------------|-----------------|-------|

| CANL1 and CANH         | H1 Pins (Continued)                                                                                                                                                    |                                   |               | 1             | 1               | 1     |

| R <sub>IN_UPWR1</sub>  | CANL1, CANH1 Input Resistance, $V_{CANL1} = V_{CANH1} = \pm 12 V$                                                                                                      | 10                                | _             | _             | kΩ              |       |

| C <sub>CAN CAP1</sub>  | CANL1, CANH1 Input Capacitance                                                                                                                                         | _                                 | 20            | _             | pF              | (4)   |

| C <sub>DIF_CAP1</sub>  | CANL1, CANH1 Differential Input Capacitance                                                                                                                            | _                                 | 10            | _             | pF              | (4)   |

| STB2 INPUT             |                                                                                                                                                                        |                                   |               |               |                 |       |

| V <sub>STB2</sub>      | Input Voltages <ul> <li>High level Input voltage</li> <li>Low level input voltage</li> <li>Input threshold hysteresis</li> </ul>                                       | 0.7 x V <sub>IO</sub><br>-<br>200 | -<br>-        | _<br>0.3<br>_ | V<br>V<br>mV    |       |

| R <sub>PU-STB2</sub>   | Pull-up Resistor to V <sub>IO</sub>                                                                                                                                    | -                                 | 100           | -             | kΩ              |       |

| XD2 INPUT              |                                                                                                                                                                        |                                   |               | •             | •               |       |

| V <sub>TXD2</sub>      | Input Voltages <ul> <li>High level Input voltage</li> <li>Low level input voltage</li> <li>Input threshold hysteresis</li> </ul>                                       | 0.7 x V <sub>IO</sub><br>-<br>200 | _<br>_<br>300 | _<br>0.3<br>_ | V<br>V<br>mV    |       |

| R <sub>PU-TXD2</sub>   | Pull-up Resistor to V <sub>IO</sub>                                                                                                                                    | 5.0                               | _             | 50            | kΩ              |       |

| RXD2 OUTPUT            |                                                                                                                                                                        |                                   |               | •             | •               |       |

| I <sub>RXD2</sub>      | Output Current<br>• RXD2 high, VRXD2 high = V <sub>IO</sub> - 0.4 V<br>• RXD2 low, VRXD2 high = 0.4 V                                                                  | -5.0<br>1.0                       | -2.5<br>2.5   | -1.0<br>5.0   | mA              |       |

| R <sub>PU-RXD2</sub>   | Pull-up Resistor to ${\rm V}_{\rm IO}$ (in Standby mode, without toggling - no wake-up report)                                                                         | 25                                | 50            | 90            | kΩ              |       |

| CANL2 and CANH         | H2 Pins                                                                                                                                                                |                                   |               | •             |                 | •     |

| V <sub>REC2</sub>      | Recessive Voltage, TXD2 high, no load<br>• CANL2 recessive voltage<br>• CANH2 recessive voltage                                                                        | 2.0<br>2.0                        | 2.5<br>2.5    | 3.0<br>3.0    | v               |       |

| V <sub>DIFF_REC2</sub> | CANH2 - CANL2 Differential Recessive Voltage, TXD2 high, no load                                                                                                       | -50                               | _             | 50            | mV              |       |

| V <sub>REC_SM2</sub>   | Recessive voltage, sleep mode, no load <ul> <li>CANL2 recessive voltage</li> <li>CANH2 recessive voltage</li> </ul>                                                    | -0.1<br>-0.1                      | -             | 1.0<br>1.0    | v               |       |

| V <sub>DOM2</sub>      | <ul> <li>Dominant Voltage, TXD2 low (t &lt; TX<sub>DOM</sub>), R<sub>L</sub> = 45 Ω to 65 Ω</li> <li>CANL2 dominant voltage</li> <li>CANH2 dominant voltage</li> </ul> | 0.5<br>2.75                       | _<br>_        | 2.25<br>4.5   | V               |       |

| V <sub>DIFF_DOM2</sub> | CANH2 - CANL2 Differential Dominant Voltage, R_L = 45 $\Omega$ to 65 $\Omega, {\rm TxD2}_{\rm LOW}$                                                                    | 1.5                               | 2.0           | 3.0           | V               |       |

| V <sub>SYM2</sub>      | Driver symmetry CANH2 + CANL2                                                                                                                                          | 0.9                               | 1.0           | 1.1           | V <sub>DD</sub> |       |

| I <sub>LIM2</sub>      | Current Limitation, TXD2 low (t < TX <sub>DOM</sub> )<br>• CANL2 current limitation, CANL2 5.0 V to 28 V<br>• CANH2 current limitation, CANH2 = 0.0 V                  | 40<br>-100                        | -             | 100<br>-40    | mA              |       |

| $V_{DIFF_THR2}$        | CANH2 - CANL2 Differential Input Threshold                                                                                                                             | 0.5                               | -             | 0.9           | V               |       |

| $V_{DIFF_HYS2}$        | CANH2 - CANL2 Differential Input Voltage Hysteresis                                                                                                                    | 50                                | -             | 400           | mV              |       |

| $V_{DIFF_THR_S2}$      | CANH2 - CANL2 Differential Input Threshold, in Standby mode                                                                                                            | 0.4                               | _             | 1.15          | V               |       |

| V <sub>CM2</sub>       | Common Mode Voltage                                                                                                                                                    | -15                               | _             | 20            | V               |       |

#### Table 5. Static Electrical Characteristics (continued)

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, 2.8 V  $\leq$  V<sub>IO</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0.0 V, R on CANx bus (R<sub>L</sub>) = 60  $\Omega$ , unless otherwise noted. Typical values noted reflect the approximate parameter at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                 | Characteristic                                                                                                                                                                           | Min.       | Тур. | Max.     | Unit | Notes |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|----------|------|-------|

| CANL2 and CAN          | H2 Pins                                                                                                                                                                                  |            |      |          |      | 1     |

| R <sub>IN2</sub>       | Input Resistance <ul> <li>CANL2 input resistance</li> <li>CANH2 input resistance</li> </ul>                                                                                              | 5.0<br>5.0 |      | 50<br>50 | kΩ   |       |

| R <sub>IN_DIFF2</sub>  | CANH2, CANL2 Differential Input Resistance                                                                                                                                               | 10         | -    | 100      | kΩ   |       |

| R <sub>IN_MATCH2</sub> | Input Resistance Matching                                                                                                                                                                | -3.0       | -    | 3.0      | %    |       |

| I <sub>IN_UPWR2</sub>  | CANL2 or CANH2 input current, device unpowered, VDD = VIO = 0 V ,<br>VCANL2 and VCANH2 0.0 to 5.0 V range<br>• VDD connected with R=0KOhm to GND<br>• VDD connected with R=47KOhm to GND | -10<br>-10 | -    | 10<br>10 | μΑ   |       |

| R <sub>IN_UPWR2</sub>  | CANL2, CANH2 Input Resistance, VCANL2 = VCANH2= ±12 V                                                                                                                                    | 10         | -    | -        | kΩ   |       |

| C <sub>CAN_CAP2</sub>  | CANL2, CANH2 Input Capacitance (guaranteed by design and characterization)                                                                                                               | -          | 20   | -        | pF   |       |

| C <sub>DIF_CAP2</sub>  | CANL2, CANH2 Differential Input Capacitance                                                                                                                                              | -          | 10   | -        | pF   | (4)   |

| T <sub>SD</sub>        | Thermal Shutdown                                                                                                                                                                         | 150        | 185  | -        | °C   |       |

Notes

4. Guaranteed by design and characterization

### 4.3.2 Dynamic Electrical Characteristic

### Table 6. Dynamic Electrical Characteristics

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, 2.8 V  $\leq$  V<sub>IO</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, R on CANx bus (R<sub>L</sub>) = 60  $\Omega$ , unless otherwise noted. Typical values noted reflect the approximate parameter at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                 | Characteristic                                                | Min. | Тур. | Max. | Unit | Notes |  |  |  |

|------------------------|---------------------------------------------------------------|------|------|------|------|-------|--|--|--|

| TIMING PARAME          | MING PARAMETERS (Continued)                                   |      |      |      |      |       |  |  |  |

| tX <sub>DOM</sub>      | TXD DOM                                                       | 2.5  | -    | 16   | ms   | (5)   |  |  |  |

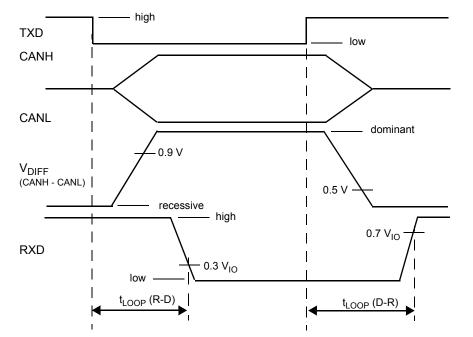

| t <sub>LOOP</sub>      | Т Loop                                                        | -    | -    | 255  | ns   |       |  |  |  |

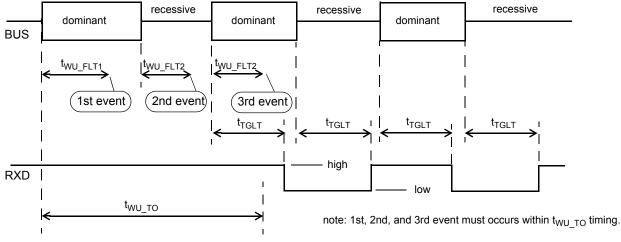

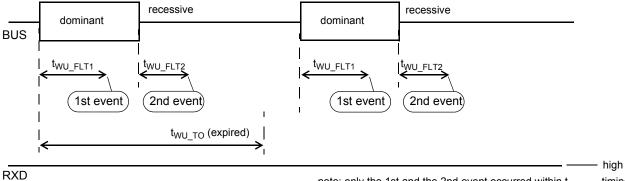

| t <sub>WU_FLT1</sub>   | TWU Filter1                                                   | 0.5  | -    | 5.0  | μs   |       |  |  |  |

| t <sub>WU_FLT2</sub>   | TWU Filter2                                                   | 0.08 | -    | 1.0  | μs   |       |  |  |  |

| t <sub>TGLT</sub>      | Tdelay During Toggling                                        | -    | -    | 1.5  | μs   |       |  |  |  |

| t <sub>wu_то</sub>     | Twake-up Timeout                                              | 1.5  | -    | 7.0  | ms   |       |  |  |  |

| t <sub>DELAY_PWR</sub> | Delay Between Power-up and Device Ready                       | -    | 120  | 300  | μs   |       |  |  |  |

| t <sub>DELAY_SN</sub>  | Transition Time from Standby to Normal mode (STB high to low) | _    | _    | 40   | μs   |       |  |  |  |

Notes

5. 33CM0902 version only

#### CM0902

Figure 3. Timing Test Circuit

Figure 4. CAN Timing Diagram

Figure 5. Wake-up Pattern Timing Illustration

note: only the 1st and the 2nd event occurred within  $t_{WU\_TO}$  timing.

Figure 6. Timeout Wake-up Timing Illustration

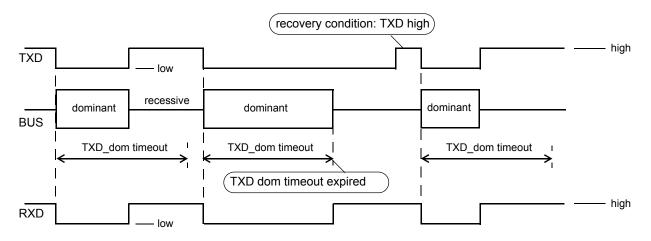

Figure 7. TXD Dominant Timeout Detection Illustration

# 4.4 Operating Conditions

This section describes the operating conditions of the device. Conditions apply to all the following data, unless otherwise noted.

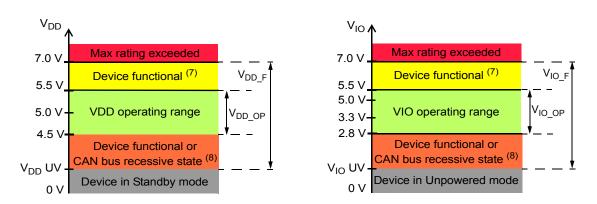

#### Table 7. Operating Conditions

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol             | Ratings                                      | Min.               | Max. | Unit | Notes |

|--------------------|----------------------------------------------|--------------------|------|------|-------|

| V <sub>DD_F</sub>  | Functional Operating V <sub>DD</sub> voltage | V <sub>DD_UV</sub> | 7.0  | V    | (6)   |

| V <sub>DD_OP</sub> | Parametric Operating V <sub>DD</sub> voltage | 4.5                | 5.5  | V    |       |

| V <sub>IO_F</sub>  | Functional Operating V <sub>IO</sub> voltage | V <sub>IO_UV</sub> | 7.0  | V    | (6)   |

| V <sub>IO_OP</sub> | Parametric Operating V <sub>IO</sub> voltage | 2.8                | 5.5  | V    |       |

Notes

6. Functional operating voltage is defined as device functional or CAN in recessive state

#### Notes

Figure 8. Supply Voltage Operating Range

- 7. Device functional: Device can operate in this voltage range without damage. Electrical characteristics are not fully guaranteed in this range.

- 8. Device functional or CAN bus recessive state: Device is either functional (see Note 1), or is maintained in recessive state. No false dominant state on CAN bus; dominant state is only controlled by TXDx low level.

# 5 General IC Functional Description and Application Information

The CM0902 is a SMARTMOS two channel high-speed CAN transceiver, providing the physical interface between the CAN protocol controller of an MCU and the physical two-wire CAN bus, featuring CAN bus wake-up on each CAN channel and TXD dominant timeout (33CM0902 version only). The two CAN physical layers are packaged in a 14-pin SOIC with market standard pin out, and offer excellent EMC and ESD performance without the need for external filter components. These meet the ISO 11898-2 and ISO11898-5 standards, and provide low leakage on CAN bus while unpowered.

The device is supplied from VDD, while VIO allows automatic operation with 5.0 V and 3.3 V microcontrollers interface.

## 5.1 Features

- · Very low current consumption in standby mode

- Automatic adaptation to 3.3 V or 5.0 V MCU communication

- · Standby mode with remote CAN wake-up

- · Pin and function compatible with market standard

- Cost efficient robustness:

- High system level ESD performance

- Very high electromagnetic Immunity and Iow electromagnetic emission without common mode choke or other external components.

- · Fail-safe behaviors:

- TXD Dominant timeout (33CM0902 only)

- Ideal passive behavior when unpowered, CAN bus leakage current <10  $\mu\text{A}.$

- +  $V_{DD}$  and  $V_{IO}$  monitoring

## 5.2 Functional Block Diagram

## 5.3 Functional Description

### 5.3.1 V<sub>DD</sub> Power Supply

This is the supply for the CANHx and CANLx bus drivers, the bus differential receiver and the bus biasing voltage circuitry. V<sub>DD</sub> is monitored for undervoltage conditions. See Fail-safe Mechanisms.

When the device is in standby mode, the consumption on VDD is extremely low (Refer to IVDD).

## 5.3.2 V<sub>IO</sub> Digital I/O Power Supply

This is the supply for the TXDx, RXDx, and STBx digital input outputs pins.  $V_{IO}$  also supplies the low power differential wake-up receivers and filter circuitry. This allows detecting and reporting bus wake-up events with device supplied only from  $V_{IO}$ .  $V_{IO}$  is monitored for undervoltage conditions. See Fail-safe Mechanisms.

When the device is in Standby mode, the consumption on V<sub>IO</sub> is extremely low (Refer to IVIO).

### 5.3.3 STB1 and STB2

STBx are the input pins to control the CANx interface mode. When STBx is high or floating, the respective CANx interface is in Standby mode. When STBx is low, the CANx interface is set in Normal mode. STBx has an internal pull-up to the VIO pin, so if STBx is left open, the CANx is set to the predetermined Standby mode.

## 5.3.4 TXD1 and TXD2

TXDx is the device input pin to control the CANx bus level. In the application, this pin is connected to one of the microcontroller's transmit pins. When TXDx is high or floating, the CANHx and CANLx drivers are OFF in Normal mode, setting the bus in a recessive state. When TXDx is low, the CANHx and CANLx drivers are activated and the bus is set to a dominant state. TXDx has a built-in timing protection on the 33CM0902 version, which disables the bus when TXDx is dominant for more than tX<sub>DOM</sub>.

In Standby mode, TXDx has no effect on the respective CANx interface.

### 5.3.5 RXD1 and RXD2

RXDx is the bus output level report pin. This pin connects to one of the microcontroller's receive pins in the application. RXDx is a pushpull structure in Normal mode. When the respective CANx bus is in a recessive state, RXDx is high, and low when the bus is dominant. In Standby mode, the push-pull structure is disabled, RXDx is pulled up to VIO via a resistor ( $R_{PU-RXD1}$ ), and is in a high level. When the bus wake-up is detected, the push-pull structure resumes and RXDx reports a wake-up via a toggling mechanism (refer to Figure 5).

## 5.3.6 CANH1 / CANL1 and CANH2 / CANL2

These are the CAN bus pins and each channel 1 or 2 is fully independent from each other. CANLx is a low-side driver to GND, and CANHx is a high-side driver to VDD. In Normal mode and TXDx high, the CANHx and CANLx drivers are OFF, and the voltage at CANHx and CANLx is approx. 2.5 V, provided by the internal bus biasing circuitry. When TXDx is low, CANLx is pulled to GND and CANHx to VDD, creating a differential voltage on the CAN bus.

CANHx and CANLx drivers are OFF in Standby mode, and pulled to GND via the CANx interface R<sub>IN</sub> resistors (ref to parameter Input Resistance). CANHx and CANLx are high-impedance with extremely low leakage to GND in device unpowered mode, making the device ideally passive when unpowered. CANHx and CANLx have integrated ESD protection and extremely high robustness versus external disturbance, such as EMC and electrical transients. These pins have current limitation and thermal protection.

# 6 Functional Operation

# 6.1 Operating Modes

The CM0902 provides two CAN, each one capable of independently operating in two modes: Standby and Normal.

### 6.1.1 Normal Mode

This mode is selected when the STBx pin is low. In this mode, the device is able to transmit information from TXDx to the bus and report the bus level on the RXDx pin. When TXDx is high, CANHx and CANLx drivers are off and the bus is in the recessive state (unless it is in an application where another device drives the bus to the dominant state). When TXDx is low, CANHx and CANLx drivers are ON and the bus is in the dominant state.

### 6.1.2 Standby Mode

This mode is selected when the STBx pin is high or floating. The device is not able to transmit information from TXDx to the bus and it cannot report accurate bus information in this mode. The device can only report bus wake-up events via the RXDx toggling mechanism. When both CAN interfaces are in Standby mode, the power consumption from  $V_{DD}$  and  $V_{IO}$  is extremely low. The CANHx and CANLx pins are pulled to GND via the internal  $R_{IN}$  resistors in this mode.

### 6.1.2.1 Wake-up Mechanism

The CM0902 includes bus monitoring circuitry to detect and report bus wake-ups. To activate a wake-up report, three events must occur on the CAN bus:

- event 1: a dominant level for a time longer than  $t_{WU\ FLT1}$  followed by

- event 2: a recessive level (event 2) longer than  $t_{WU\ FLT2}$  followed by

- event 3: a dominant level (event 3) longer than  $t_{WU\ FLT2}$ .

The RXD pin reports the bus state (bus dominant => RXD low, bus recessive => RXD high). The delay between bus dominant and RXD low, and bus recessive and RXD high is longer than in Normal mode (refer to  $t_{TGLT}$ ). The three events must occur within the  $t_{WU_TO}$  timeout.

Figure 5 "Wake-up Pattern Timing Illustration" illustrates the wake-up detection and reporting (toggling) mechanism.

If the three events do not occur within the  $T_{WU_TO}$  timeout, the wake-up and toggling mechanism are not activated. This is illustrated in <u>Figure 6</u>. The three events and the timeout function avoid a permanent dominant state on the bus which would generate a permanent wake-up situation, and prevent the system from entering into Low-power mode.

### 6.1.3 Unpowered Mode

When  $V_{IO}$  is below  $V_{IO UV}$ , the device is in unpowered mode. Both CAN buses is in high-impedance and not able to transmit, receive, or report bus wake-up events through any of the buses.

## 6.2 Fail-safe Mechanisms

The device implements various protection, detection, and predictable fail-safe mechanisms explained below.

### 6.2.1 STB and TXD Input Pins

The STBx input pin has an internal integrated pull-up structure to the VIO supply pin. If STBx is open, the respective CANx interface is set to Standby mode to ensure predictable behavior and minimize system current consumption.

The TXDx input pin also has an internal integrated pull-up structure to the VIO supply pin. If TXDx is open, the CANx driver is set to the recessive state to minimize current consumption and ensure no false dominant bit is transmitted on the bus.

### 6.2.2 TXD Dominant Timeout Detection

The 33CM0902 device implements a TXD dominant timeout detection and protection mechanism. If TXDx is set low for a time longer than the tX<sub>DOM</sub> parameter, the CANx drivers are disabled and the CANx bus returns to the recessive state. This prevents the bus from being set to the dominant state permanently in case a fault sets the TXDx input to low level permanently. The device recovers when a high level is detected on TXDx (Refer to Figure 7).

### 6.2.3 CAN Current Limitation

The current flowing in and out of the CANHx and CANLx driver is limited to a maximum of 100 mA, in case of a short-circuit (parameter for I<sub>LIM1</sub>).

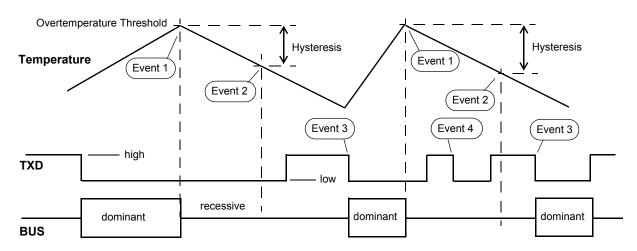

### 6.2.4 CAN Overtemperature

If the driver temperature exceeds  $T_{SD}$ , the driver turns off to protect the device. A hysteresis is implemented in this protection feature. The device overtemperature and recovery conditions are shown in <u>Figure 10</u>. The driver remains disabled until the temperature has fallen below the OT threshold minus the hysteresis and a TXD high to low transition is detected. Since both CAN interfaces are fully independent, each driver requires a high to low transition of its own TXDx pin to re-enable the CAN driver.

Event 1: overtemperature detection. CAN driver disabled.

Event 2: temperature falls below "overtemperature. threshold minus hysteresis" => CAN driver remains disabled.

Event 3: temperature below "overtemperature. threshold minus hysteresis" and TxD high to low transition => CAN driver enabled.

Event 4: temperature above "overtemperature. threshold minus hysteresis" and TxD high to low transition => CAN driver remains disabled.

#### Figure 10. Overtemperature Behavior

## 6.2.5 V<sub>DD</sub> and V<sub>IO</sub> Supply Voltage Monitoring

The device monitors the  $V_{\text{DD}}$  and  $V_{\text{IO}}$  supply inputs.

The device is set in Standby mode if  $V_{DD}$  falls below  $V_{DD UV}$  (VDD\_UV). This ensures a predictable behavior due to the loss of  $V_{DD}$ . CAN drivers, receiver, or bus biasing cannot operate any longer. In this case, the bus wake-up is available as  $V_{IO}$  remains active.

If  $V_{IO}$  falls below  $V_{IO UV}$  (VIO\_UV), the device is set to an unpowered condition. This ensures a predictable behavior due to the loss of  $V_{IO}$ , CAN drivers, receivers, or bus biasing cannot operate any longer. This sets the bus in high-impedance and in ideal passive condition.

### 6.2.6 Bus Dominant State Behavior in Standby Mode

When the CAN interface is in Standby mode, a bus dominant condition due to a short-circuit or a fault in any of the CAN nodes, does not generate a permanent wake-up event, since the specific wake-up sequence and timeout protect the device from waking-up with an unwanted event.

#### CM0902

# 6.3 Device Operation Summary

The following table summarizes the CAN interface operation and the state of the input/output pins, depending on the operating mode and power supply conditions.

#### STANDBY and NORMAL MODES

| MODE    | Description                           | V <sub>DD</sub><br>Range | V <sub>IO</sub><br>Range | STBx                | TXDx                                                             | RXDx                                                                               | CANx                                                                                                                                                                              | Wake-up  |

|---------|---------------------------------------|--------------------------|--------------------------|---------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Normal  | Nominal supply<br>and normal<br>mode  | from 4.5 V<br>to 5.5 V   | from 2.8 V<br>to 5.5 V   | Low                 | TXD High<br>=> bus<br>recessive<br>TXD Low =><br>bus<br>dominant | Report CAN state<br>(bus recessive =><br>RXD high, bus<br>dominant => RXD<br>low). | CANH and CANL drivers controlled<br>by TXD input.<br>Differential receiver reports the bus<br>state on RXD pin.<br>Biasing circuitry provides approx<br>2.5 V in recessive state. | Disabled |

| Standby | Nominal supply<br>and standby<br>mode | from 0.0 V<br>to 5.5 V   | from 2.8 V<br>to 5.5 V   | High or<br>floating | No effect. on<br>CAN bus.                                        | Report bus wake up<br>via toggling<br>mechanism.                                   | CAN driver and differential receiver<br>disabled.<br>Bus biased to GND via internal R <sub>IN</sub><br>resistors.                                                                 | Enabled  |

#### UNDERVOLTAGE and LOSS OF POWER CONDITIONS

|                                             | Device in standby mode due to loss of $V_{DD}$ ( $V_{DD}$ falls below $V_{DD}$ uv)             | from 0.0 to<br>V <sub>DD_UV</sub> .<br>(10) | from 2.8 V<br>to 5.5 V<br>(11)      | X<br>(9) | Х | Report bus wake up             | CAN driver and differential receiver<br>disabled.<br>Bus biased to GND via internal R <sub>IN</sub><br>resistors. | Enabled        |

|---------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------|----------|---|--------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------|

| Unpowered<br>due to V <sub>IO</sub><br>loss | Device in<br>unpowered<br>state due to low<br>V <sub>IO</sub> . CAN bus<br>high-<br>impedance. | (10)                                        | from 0.0 V<br>to V <sub>IO_UV</sub> | Х        |   | down to V <sub>IO</sub> approx | CAN driver and differential receiver<br>disabled.<br>High-impedance, with ideal passive<br>behavior.              | Not available. |

Notes

9. STBx pin has no effect. CANx Interface enters in Standby mode.

10.  $V_{DD}$  consumption < 10 uA down to  $V_{DD}$  approx 1.5 V.

11.  $V_{IO}$  consumption < 10 uA down to  $V_{IO}$  approx 1.5 V. If STB is high or floating.

# 7 Typical Applications

## 7.1 Application Diagrams

Figure 11. Single Supply Typical Application Schematic

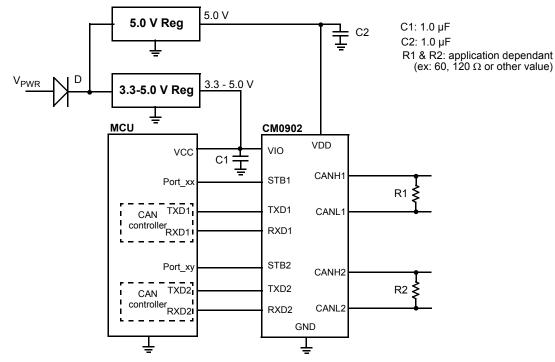

Figure 12. Dual Supply Typical Application Schematic

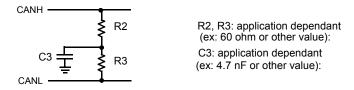

Figure 13. Example of Bus Termination Options

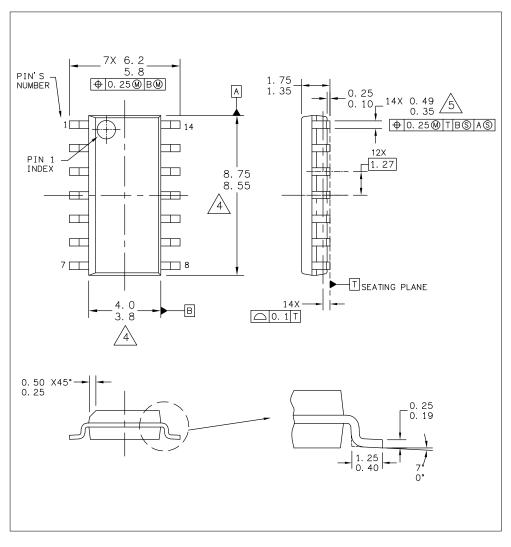

# 8 Packaging

# 8.1 Package Mechanical Dimensions

Package dimensions are provided in package drawings. To find the most current package outline drawing, go to www.freescale.com and perform a keyword search for the drawing's document number.

### Table 8. Packaging Information

| Package      | Suffix | Package Outline Drawing Number |  |  |

|--------------|--------|--------------------------------|--|--|

| 14-Pin SOICN | EF     | 98ASB42565B                    |  |  |

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                                  |           |              | ): 98ASB42565B   | REV: J      |

| 14LD SOIC N/B, 1.27 PIT<br>CASE-OUTLINE                 |           | CASE NUMBER  | R: 751A-04       | 04 DEC 2007 |

|                                                         |           | STANDARD: JE | CCDEC MS-012AB   |             |

| NO | TES:                                                                                                                                                                                                                                                  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | DIMENSIONS ARE IN MILLIMETERS.                                                                                                                                                                                                                        |

| 2. | DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.                                                                                                                                                                                                    |

| 3. | DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY. DATUM T IS A SURFACE.                                                                                                                               |

| 4  | THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD<br>FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS<br>DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT<br>THE PLASTIC BODY. |

| ß. | THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTOAL IN EXCESS OF THE LEAD WIDTH AT MAXIMUM MATERIAL CONDITION.                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                                                       |

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO  | ): 98ASB42565B   | REV: J      |

| 14LD SOIC N/B, 1.27 PITC<br>CASE-OUTLINE                |           | CASE NUMBER  | R: 751A-04       | 04 DEC 2007 |

|                                                         |           | STANDARD: JE | ECDEC MS-012AB   |             |

.

# 9 Revision History

| Revision | Date    | Description of Changes                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 6/2014  | Initial release                                                                                                                                                                                                                                                                                                                                        |

| 2.0      | 11/2014 | Data adjusted to match latest silicon                                                                                                                                                                                                                                                                                                                  |

| 3.0      | 1/2015  | Changed ordering information from PC to MC                                                                                                                                                                                                                                                                                                             |

| 4.0      | 4/2015  | <ul> <li>Added information for dual speed (up to 1 Mbit/s)</li> <li>Added V<sub>REC_SM1</sub> &amp; V<sub>REC_SM2</sub> (CANH, CANL recessive voltage, sleep mode) to Table 5</li> <li>Added driver symmetry V<sub>SYM1</sub> &amp; V<sub>SYM2</sub> to Table 5</li> <li>Updated I<sub>IN_UPWR1</sub> &amp; I<sub>IN_UPWR2</sub> in Table 5</li> </ul> |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. SMARTMOS is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2015 Freescale Semiconductor, Inc.

Document Number: CM0902 Rev. 4.0 4/2015