Sample &

Buy

LDC1101

#### SNOSD01B-MAY 2015-REVISED JULY 2015

# LDC1101 1.8 V High-Resolution, High-Speed Inductance-to-Digital Converter

Technical

Documents

#### 1 Features

- Wide Operating Voltage Range: 1.8 V to 3.3 V

- Sensor Frequency Range: 500 kHz to 10 MHz

- R<sub>P</sub> Resolution: 16-bit

- L Resolution: 16/24-bit

- 180 kSPS Conversion Rate

- **Threshold Detection Functionality**

- 1% Part-to-Part Variation in R<sub>P</sub> Measurement

- Supply Current:

- 1.4 µA Shutdown mode

- 135 µA Sleep mode

- 1.9 mA Active Mode (no sensor connected)

- Sub-micron Distance Resolution Achievable

- Remote Sensor Placement Isolating the LDC from Harsh Environments

- Robust Against Environmental Interferences such as Oil, Water, Dirt or Dust

- Minimal External Components

- Magnet-Free Operation

- Operating Temperature: -40°C to 125°C

#### 2 Applications

- High-speed Gear Counting

- High-speed Event Counting

- Motor Speed Sensing

- Knobs and Dials for Appliances, Automotive, and **Consumer Applications**

- HMI for Appliances, Automotive, and Consumer . Applications

- Buttons and Keypads

- Motor Control

- Metal Detection

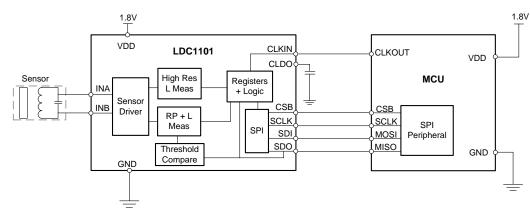

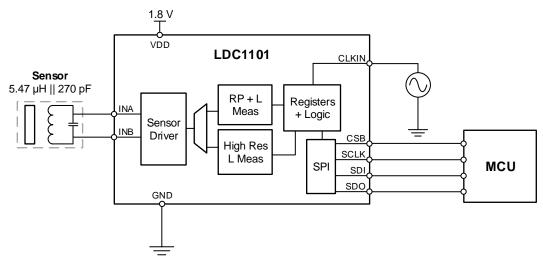

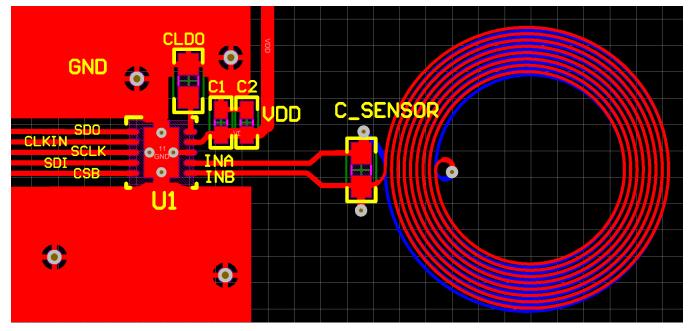

#### 4 Simplified Schematic

### 3 Description

Tools &

Software

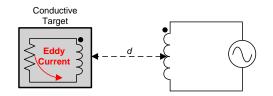

The LDC1101 is a 1.8 V to 3.3 V, high-resolution inductance-to-digital converter for short-range, highspeed, contactless sensing of position, rotation, or motion, enabling reliable, accurate measurements even in the presence of dust or dirt, making it ideal for open or harsh environments.

Support &

Community

**.**...

The LDC1101 features dual inductive measurement cores, allowing for > 150 ksps 16-bit  $R_P$  and L measurements simultaneous with a high-resolution L measurement which can sample at > 180 ksps with a resolution of up to 24 bits. The LDC1101 includes a threshold-compare function which can be dynamically updated while the device is running.

technology Inductive sensing enables precise measurement of linear/angular position, displacement, motion, compression, vibration, metal composition, and many other applications in markets including automotive, consumer, computer, industrial, medical, and communications. Inductive sensing offers better performance and reliability at lower cost than other, competing solutions.

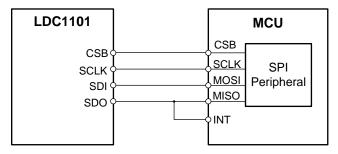

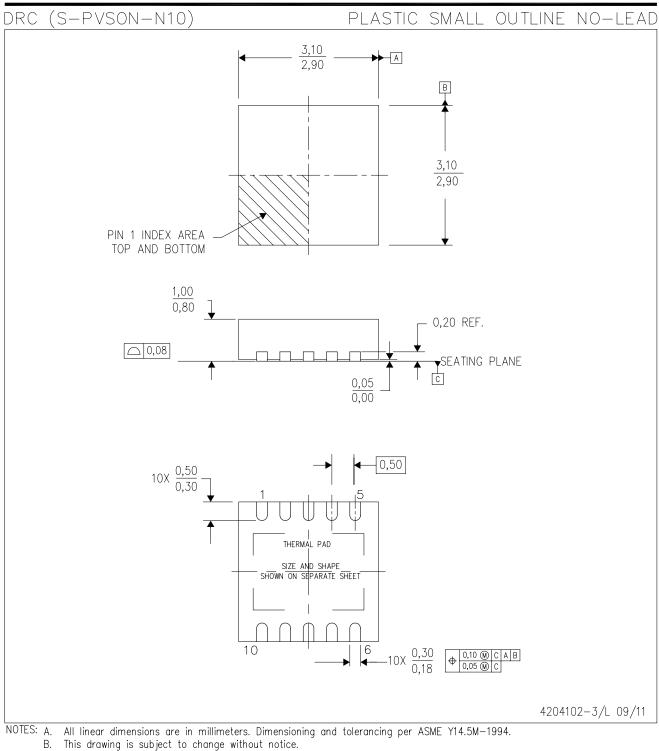

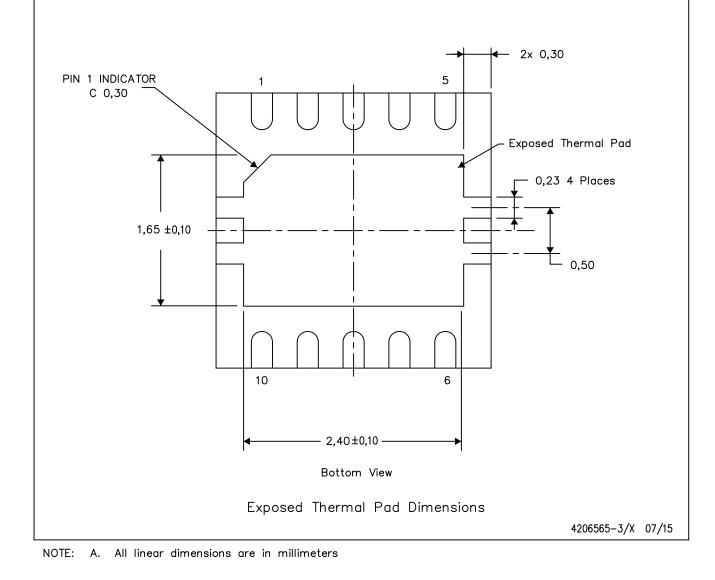

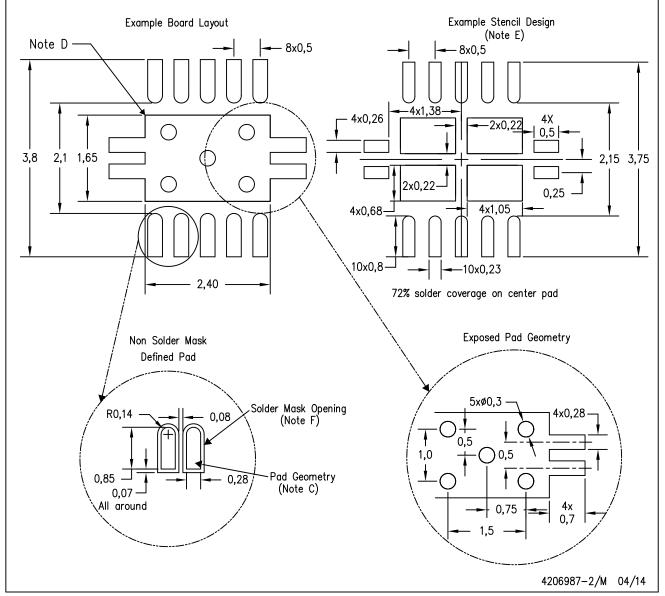

The LDC1101 offers these benefits of inductive sensing in a small 3 mm × 3 mm 10-pin VSON package. The LDC1101 can be easily configured by a microcontroller using the 4-pin SPI™.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE       | BODY SIZE (NOM)   |  |  |

|-------------|---------------|-------------------|--|--|

| LDC1101     | VSON (10) DRC | 3.00 mm × 3.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

2

# **Table of Contents**

8.4 8.5

8.6

12.1

12.2

12.3

13

9

| 1 | Feat           | tures 1                            |  |  |  |

|---|----------------|------------------------------------|--|--|--|

| 2 | Applications 1 |                                    |  |  |  |

| 3 | Des            | cription1                          |  |  |  |

| 4 | Sim            | plified Schematic1                 |  |  |  |

| 5 | Rev            | ision History 2                    |  |  |  |

| 6 | Pin            | Configuration and Functions 3      |  |  |  |

| 7 | Spe            | cifications 4                      |  |  |  |

|   | 7.1            | Absolute Maximum Ratings 4         |  |  |  |

|   | 7.2            | ESD Ratings 4                      |  |  |  |

|   | 7.3            | Recommended Operating Conditions 4 |  |  |  |

|   | 7.4            | Thermal Information 4              |  |  |  |

|   | 7.5            | Electrical Characteristics 5       |  |  |  |

|   | 7.6            | Digital Interface 5                |  |  |  |

|   | 7.7            | Timing Requirements 6              |  |  |  |

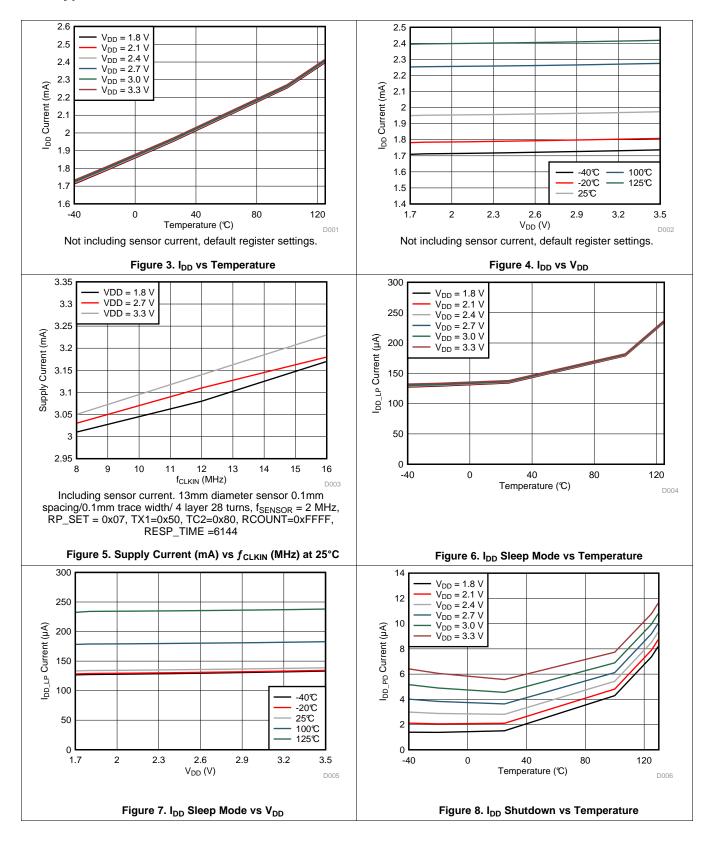

|   | 7.8            | Typical Characteristics 7          |  |  |  |

| 8 | Deta           | ailed Description                  |  |  |  |

|   | 8.1            | Overview                           |  |  |  |

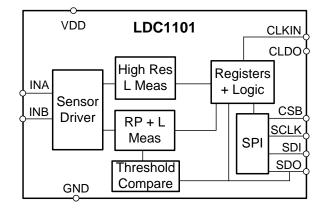

|   | 8.2            | Functional Block Diagram 9         |  |  |  |

|   | 8.3            | Feature Description9               |  |  |  |

|   |                |                                    |  |  |  |

| 5 | Revision | History |

|---|----------|---------|

|---|----------|---------|

| C | Changes from Revision A (June 2015) to Revision B                                 |    |  |

|---|-----------------------------------------------------------------------------------|----|--|

| • | Changed Register type and reset values for some fields which where incomplete     | 15 |  |

| • | Changed NAME to INTB_MODE                                                         | 20 |  |

| • | Changed DRDY to INTB in INTB2SDO field descriiption                               | 20 |  |

| • | Changed RP Threshold and L Threshold field names in RP_HI_LON and L_HI_LON fields | 23 |  |

| • | Changed Incorrect resistance value                                                | 40 |  |

| • | Changed Calculations of reference count setting                                   |    |  |

#### Changes from Original (May 2015) to Revision A

| Added full datasheet to replace | the Product Preview |

|---------------------------------|---------------------|

|---------------------------------|---------------------|

Application and Implementation ...... 29

10 Power Supply Recommendations ...... 44 11 Layout...... 44 11.1 Layout Guidelines ..... 44 11.2 Layout Example ..... 45 12 Device and Documentation Support ...... 46

> Device Support ..... 46 Documentation Support ...... 46

Community Resources...... 46

12.4 Trademarks ..... 46 12.5 Electrostatic Discharge Caution ...... 46

Mechanical, Packaging, and Orderable

EXAS

STRUMENTS

# Information ...... 46

#### Page

Copyright © 2015, Texas Instruments Incorporated

#### LDC1101 SNOSD01B-MAY 2015-REVISED JULY 2015

### 6 Pin Configuration and Functions

| DRC Package<br>10-Pin VSON<br>Top View |      |     |                                              |      |  |  |

|----------------------------------------|------|-----|----------------------------------------------|------|--|--|

| SDO/INTB                               | 1i   |     | <u>    10    </u>                            | CLDO |  |  |

| CLKIN                                  |      |     | 9                                            | VDD  |  |  |

| SCLK                                   | _3_1 | DAP | <u>    8                                </u> | GND  |  |  |

| SDI                                    | 4!   |     |                                              | INA  |  |  |

| CSB                                    |      |     | 6                                            | INB  |  |  |

#### **Pin Functions**

| PIN      |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                               |  |

|----------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO. | ITPE                | DESCRIPTION                                                                                                                                               |  |

| CLDO     | 10  | Р                   | Internal LDO bypassing pin. A 15 nF capacitor must be connected from this pin to GND.                                                                     |  |

| CLKIN    | 2   | I                   | External time-base Clock Input                                                                                                                            |  |

| CSB      | 5   | I                   | SPI CSB. Multiple devices can be connected on the same SPI bus and CSB can be used to uniquely select desired device                                      |  |

| DAP      | _   | _                   | Connect to Ground for improved thermal performance <sup>(2)</sup>                                                                                         |  |

| GND      | 8   | G                   | round                                                                                                                                                     |  |

| INA      | 7   | А                   | xternal LC tank – connected to external LC tank                                                                                                           |  |

| INB      | 6   | А                   | External LC tank – connected to external LC tank                                                                                                          |  |

| SCLK     | 3   | I                   | PI Clock Input                                                                                                                                            |  |

| SDI      | 4   | I                   | SPI Data Input – connect to MOSI of SPI master                                                                                                            |  |

| SDO/INTB | 1   | 0                   | SPI Data Output/INTB – Connect to MISO of SPI Master. When CSB is high, this pin is High-Z. Alternatively, this pin can be configured to function as INTB |  |

| VDD      | 9   | Р                   | Power Supply                                                                                                                                              |  |

(1) P= Power, G=Ground, I=Input, O=Output, A=Analog

(2) There is an internal electrical connection between the exposed Die Attach Pad (DAP) and the GND pin of the device. Although the DAP can be left floating, for best performance the DAP should be connected to the same potential as the device's GND pin. Do not use the DAP as the primary ground for the device. The device GND pin must always be connected to ground.

### 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                         | MIN  | MAX                  | UNIT |

|------------------|-----------------------------------------|------|----------------------|------|

| $V_{DD}$         | Supply voltage range                    |      | 3.6                  | V    |

| V                | Voltage on INA, INB                     | -0.3 | 2.3                  | V    |

| Vi               | Voltage on CLDO                         | -0.3 | 1.9                  | V    |

|                  | Voltage on any other pin <sup>(2)</sup> | -0.3 | V <sub>DD</sub> +0.3 | V    |

| $T_{J}$          | Junction temperature                    | -55  | 125                  | °C   |

| T <sub>stg</sub> | Storage temperature                     | -65  | 125                  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Maximum voltage across any two pins is  $V_{DD}$ +0.3.

### 7.2 ESD Ratings

|                                               |                                                                   |                                                                                | VALUE | UNIT |

|-----------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic<br>discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000                                                                          | V     |      |

|                                               | discharge                                                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                      | MIN  | NOM MAX | UNIT |

|----------|----------------------|------|---------|------|

| $V_{DD}$ | Supply voltage       | 1.71 | 3.46    | V    |

| TJ       | Junction temperature | -40  | 125     | °C   |

#### 7.4 Thermal Information

|                       |                                              | LDC1101    |      |  |

|-----------------------|----------------------------------------------|------------|------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | DRC (VSON) | UNIT |  |

|                       |                                              | 10 PINS    |      |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 44.2       | °C/W |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 50.1       | °C/W |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 19.6       | °C/W |  |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.7        | °C/W |  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 19.8       | °C/W |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.4        | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 7.5 Electrical Characteristics

Over recommended operating conditions unless otherwise noted.  $V_{DD}$  = 1.8 V,  $T_A$  = 25°C.

|                        | PARAMETER                                                 | TEST CONDITION <sup>(1)</sup>                                                                     | MIN <sup>(2)</sup> | TYP <sup>(3)</sup>                          | MAX <sup>(2)</sup> | UNIT            |

|------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------|--------------------|-----------------|

| POWER                  |                                                           | · · · · · · · · · · · · · · · · · · ·                                                             |                    |                                             |                    |                 |

| V <sub>DD</sub>        | Supply voltage                                            |                                                                                                   | 1.71               |                                             | 3.46               | V               |

| I <sub>DD</sub>        | Supply current                                            | START_CONFIG= 0x00, no sensor connected                                                           |                    | 1.9                                         | 2.7                | mA              |

| I <sub>DDS</sub>       | Supply current including sensor<br>current                | $f_{\text{CLKIN}}$ = 16 MHz, $f_{\text{SENSOR}}$ = 2 MHz,<br>START_CONFIG = 0x00                  |                    | 3.2                                         |                    | mA              |

| IDDSL                  | Sleep mode supply current                                 | START_CONFIG =0x01                                                                                |                    | 135                                         | 180                | μA              |

| I <sub>SD</sub>        | Shutdown mode supply current                              |                                                                                                   |                    | 1.4                                         | 6.7                | μA              |

| SENSOR                 |                                                           |                                                                                                   |                    |                                             |                    |                 |

|                        | R <sub>P</sub> Measurement part-to-part variation         | $\label{eq:RESP_TIME=6144, D_CONFIG=0x00, ALT_CONFIG=0x00, START_CONFIG=0x00, f_{SENSOR} = 2 MHz$ |                    | 1%                                          |                    |                 |

| ISENSORMAX             | Sensor maximum current drive                              | RP_MIN = b111, START_CONFIG=0x00,<br>D_CONFIG=0x00, ALT_CONFIG=0x00                               | 0.598              | 0.6                                         | 0.602              | mA              |

| I <sub>SENSORMIN</sub> | Sensor minimum current drive                              | RP_MAX = b000, RPMAX_DIS=b0,<br>START_CONFIG=0x00, D_CONFIG=0x00,<br>ALT_CONFIG=0x00              |                    |                                             | μΑ                 |                 |

| f <sub>sensor</sub>    | Sensor resonant frequency                                 | Device settings and Sensor compliant as detailed in LDC1101 R <sub>P</sub> Configuration          | 0.5                |                                             | 10                 | MHz             |

| RP <sub>RES</sub>      | R <sub>P</sub> Measurement resolution                     |                                                                                                   |                    | 16                                          |                    | bits            |

|                        | Inductance sensing resolution –<br>R <sub>P</sub> +L Mode |                                                                                                   |                    | 16                                          |                    | bits            |

| L <sub>RES</sub>       | Inductance sensing resolution –<br>LHR Mode               |                                                                                                   |                    | 24                                          |                    | bits            |

| A <sub>OSC</sub>       | Sensor oscillation amplitude                              | INA – INB, START_CONFIG=0x00,<br>D_CONFIG=0x00, ALT_CONFIG=0x00                                   |                    | 1.2                                         |                    | V <sub>PP</sub> |

| DETECTION              | l                                                         | · · · · · · · · · · · · · · · · · · ·                                                             |                    |                                             |                    |                 |

| t <sub>s_MIN</sub>     | Minimum response time (RP+L mode)                         | R <sub>P</sub> +L Mode, RESP_TIME=b010                                                            | ÷f                 | 192<br>SENSOR                               |                    | S               |

| t <sub>S_MAX</sub>     | Maximum response time (RP+L mode)                         | R <sub>P</sub> +L Mode, RESP_TIME=b111                                                            | ÷f                 | 6144<br>SENSOR                              |                    | s               |

| T <sub>s_MAX</sub>     | High Res L maximum measurement interval                   | LHR_REF_COUNT=0xFFFF,<br>START_CONFIG=0x00                                                        | ,                  | 2 <sup>20</sup> +39)<br>÷f <sub>CLKIN</sub> |                    | s               |

| SR <sub>MAXRP</sub>    | RP+L Mode maximum sample rate                             | $f_{\text{CLKIN}}$ =16 MHz, $f_{\text{SENSOR}}$ = 10 MHz,<br>RESP_TIME=b010                       |                    | 156.25                                      |                    | kSPS            |

| S <sub>RMAXL</sub>     | High Res L Mode Maximum Sample<br>Rate                    | High Resolution L Mode,<br>LHR_REF_COUNT=0x0002, <i>f</i> <sub>CLKIN</sub> =16 MHz                |                    | 183.8                                       |                    | kSPS            |

| FREQUENC               | YREFERENCE                                                |                                                                                                   |                    |                                             |                    |                 |

| f <sub>CLKIN</sub>     | Reference input frequency                                 |                                                                                                   | 1                  |                                             | 16                 | MHz             |

| DC <sub>fin</sub>      | Reference duty cycle                                      |                                                                                                   | 40%                |                                             | 60%                |                 |

| VIH                    | Input high voltage (Logic "1")                            |                                                                                                   | 0                  | .8×V <sub>DD</sub>                          |                    | V               |

| V <sub>IL</sub>        | Input low voltage (Logic "0")                             |                                                                                                   | 0                  | .2×V <sub>DD</sub>                          |                    | V               |

(1) Register values are represented as either binary (b is the prefix to the digits), or hexadecimal (0x is the prefix to the digits). Decimal values have no prefix.

(2) Limits are ensured by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are ensured through correlation using statistical quality control (SQC) method.

(3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

### 7.6 Digital Interface

|                  | PARAMETER                                                     | MIN                 | TYP                  | MAX                 | UNIT |

|------------------|---------------------------------------------------------------|---------------------|----------------------|---------------------|------|

| VOLTA            | GE LEVELS                                                     | $0.8 \times V_{DD}$ |                      |                     | V    |

| VIH              | Input high voltage (Logic "1")                                |                     |                      | $0.2 \times V_{DD}$ | V    |

| VIL              | Input low voltage (Logic "0")                                 |                     | V <sub>DD</sub> -0.3 |                     | V    |

| V <sub>OH</sub>  | Output high voltage (Logic "1", I <sub>SOURCE</sub> = 400 µA) |                     |                      | 0.3                 | V    |

| V <sub>OL</sub>  | Output low voltage (Logic "0", I <sub>SINK</sub> = 400 µA)    | -500                |                      | 500                 | nA   |

| I <sub>OHL</sub> | Digital IO leakage current                                    |                     |                      |                     |      |

Copyright © 2015, Texas Instruments Incorporated

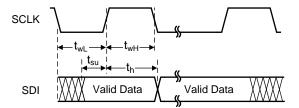

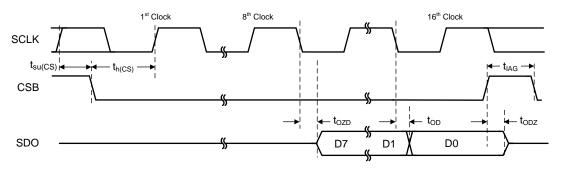

### 7.7 Timing Requirements

|                      |                                                                                                  | MIN                     | TYP     | MAX | UNIT |

|----------------------|--------------------------------------------------------------------------------------------------|-------------------------|---------|-----|------|

| t <sub>START</sub>   | Start-up time from shutdown to sleep                                                             |                         | 0.8     |     | ms   |

| t <sub>WAKE</sub>    | Wake-up time (from completion of SPI to conversion start; does not include sensor settling time) |                         | 0.04    |     | ms   |

| INTERFA              | CE TIMING REQUIREMENTS <sup>(1)</sup>                                                            |                         |         |     |      |

| $f_{\sf SCLK}$       | Serial clock frequency                                                                           |                         |         | 8   | MHz  |

| t <sub>wH</sub>      | SCLK pulse-width high                                                                            | 0.4 / f <sub>SCLK</sub> |         |     | S    |

| t <sub>wL</sub>      | SCLK pulse-width low                                                                             | 0.4 / f <sub>SCLK</sub> |         |     | S    |

| t <sub>su</sub>      | SDI setup time                                                                                   | 10                      |         |     | ns   |

| t <sub>h</sub>       | SDI hold time                                                                                    | 10                      |         |     | ns   |

| t <sub>ODZ</sub>     | SDO driven-to-tristate time                                                                      |                         |         | 25  | ns   |

| t <sub>OZD</sub>     | SDO tristate-to-driven time                                                                      |                         |         | 25  | ns   |

| t <sub>OD</sub>      | SDO output delay time                                                                            |                         |         | 20  | ns   |

| t <sub>su(CS)</sub>  | CSB setup time                                                                                   | 20                      |         |     | ns   |

| t <sub>h(CS)</sub>   | CSB hold time                                                                                    | 20                      |         |     | ns   |

| t <sub>IAG</sub>     | CSB inter-access interval                                                                        | 100                     |         |     | ns   |

| t <sub>w(DRDY)</sub> | Data ready pulse width                                                                           | 1,                      | fsensor |     | ns   |

(1) Unless otherwise noted, all limits specified at  $T_A = 25^{\circ}$ C,  $V_{DD} = 1.8$  V, 10 pF capacitive load in parallel with a 10 k $\Omega$  load on the SDO pin. Specified by design; not production tested.

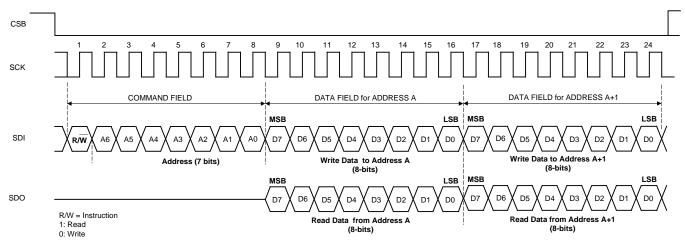

### Figure 1. Write Timing Diagram

Figure 2. Read Timing Diagram

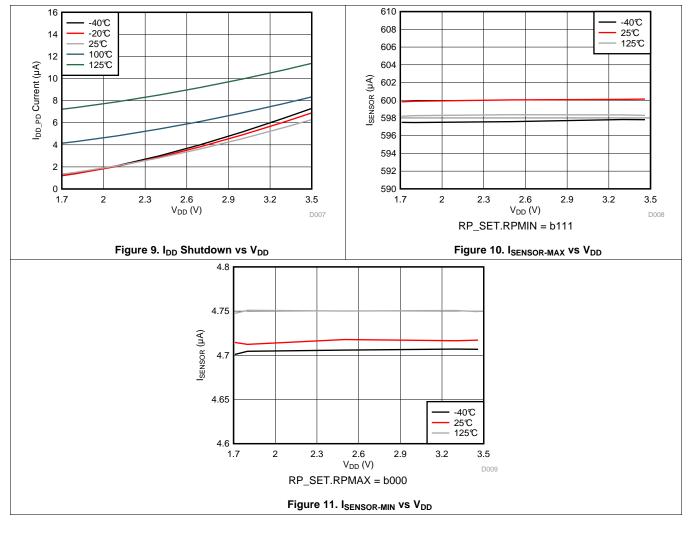

### 7.8 Typical Characteristics

## **Typical Characteristics (continued)**

### 8 Detailed Description

### 8.1 Overview

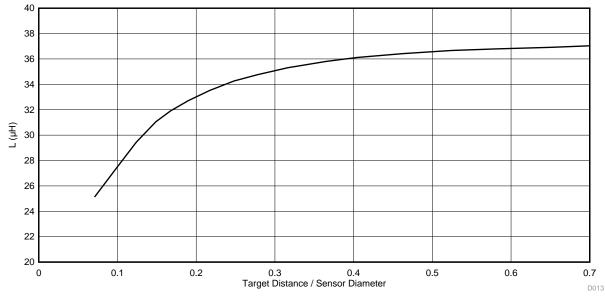

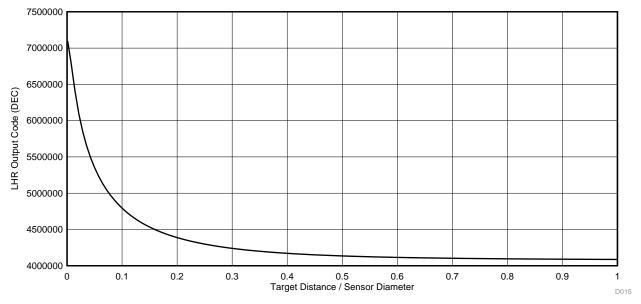

The LDC1101 is an inductance-to-digital converter which can simultaneously measure the impedance and resonant frequency of an LC resonator. The high resolution measurement capability enables this device to be used to directly measure changes in physical systems, allowing the resonator to sense the proximity and movement of conductive materials.

The LDC1101 measures the impedance and resonant frequency by regulating the oscillation amplitude in a closed-loop configuration at a constant level, while monitoring the energy dissipated by the resonator. By monitoring the amount of power injected into the resonator, the LDC1101 can determine the equivalent parallel resistance of the resonator,  $R_p$ , which it returns as a digital value.

In addition, the LDC1101 device also measures the oscillation frequency of the LC circuit by comparing the sensor frequency to a provided reference frequency. The sensor frequency can then be used to determine the inductance of the LC circuit.

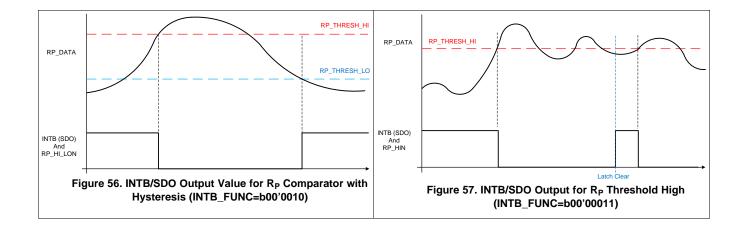

The threshold comparator block can compare the RP+L conversion results versus a programmable threshold. With the threshold registers programmed and comparator enabled, the LDC1101 can provide a switch output, reported as a high/low level on the INTB/SDO pin.

The LDC1101 device supports a wide range of LC combinations with oscillation frequencies ranging from 500 kHz to 10 MHz and R<sub>P</sub> ranging from 1.25 k $\Omega$  to 90 k $\Omega$ . The device is configured and conversion results retrieved through a simple 4-wire SPI. The power supply for the device can range from 1.8 V – 5% to 3.3 V + 5%. The only external components necessary for operation are a 15 nF capacitor for internal LDO bypassing and supply bypassing for VDD.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

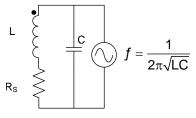

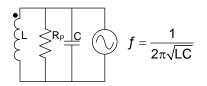

### 8.3.1 Sensor Driver

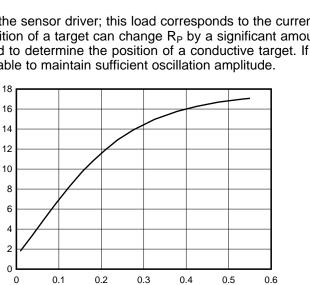

The LDC1101 can drive a sensor with a resonant frequency of 500 kHz to 10 MHz with an R<sub>P</sub> in the range of 1.25 k $\Omega$  to 90 k $\Omega$ . The nominal sensor amplitude is 1.2 V. The sensor Q should be at least 10 for R<sub>P</sub> measurements. The inductive sensor must be connected across the INA and INB pins. The resonant frequency of the sensor is set by:

$$f_{\text{SENSOR}}(\text{Hz}) = \frac{1}{2\pi\sqrt{L \times C}}$$

where

- L is the sensor inductance in Henrys, and

- C is the sensor parallel capacitance in Farads.

(1)

#### 8.4 Device Functional Modes

#### 8.4.1 Measurement Modes

The LDC1101 features two independent measurement subsystems to measure the impedance and resonant frequency of an attached sensor. The  $R_P+L$  subsystem can simultaneously measure the impedance and resonant frequency of an LC resonator, with up to 16 bits of resolution for each parameter. Refer to  $R_P+L$  *Measurement Mode* for more information on the  $R_P+L$  measurement functionality.

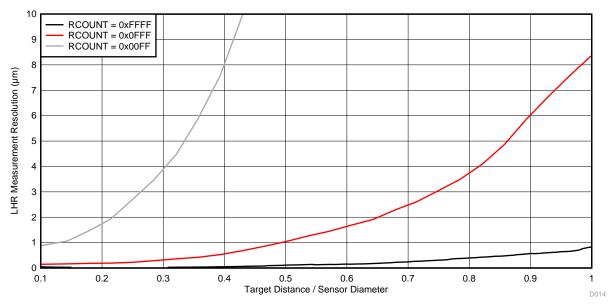

The High Resolution L (LHR) subsystem measures the sensor resonant frequency with up to 24 bits of resolution. The effective resolution is a function of the sample rate and the reference frequency supplied on the CLKIN pin. Refer to *High Resolution L (LHR) Measurement Mode* for more information on the LHR measurement functionality.

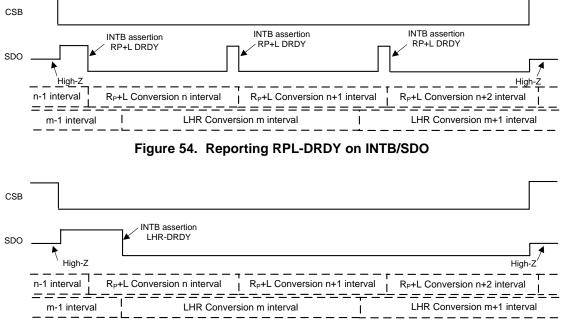

Both measurement subsystems can convert simultaneously but at different sample intervals – the completion of an  $R_P+L$  conversion will be asynchronous to the completion of a LHR conversion.

|                                         | RP+L Mode                                     | LHR Mode                                      |

|-----------------------------------------|-----------------------------------------------|-----------------------------------------------|

| R <sub>P</sub> Measurement Resolution   | 16 bits                                       | N/A                                           |

| L Measurement Resolution                | 16 bits                                       | 24 bits                                       |

| Sample Rate configuration               | Varies with $f_{SENSOR}$ , set by RESP_TIME   | Fixed and set by RCOUNT field and $f_{CLKIN}$ |

| Sample rate at highest resolution (SPS) | 244                                           | 15.3                                          |

| Maximum Sample Rate (kSPS)              | 156.25                                        | 183.9                                         |

| L Resolution at Maximum Sample rate     | 6.7 bits                                      | 6.5 bits                                      |

| Switch Output on SDO/INTB               | Available for R <sub>P</sub> or L output code | N/A                                           |

#### Table 1. Comparison of Measurement Modes

#### 8.4.2 R<sub>P</sub>+L Measurement Mode

In RP+L mode, the LDC1101 will simultaneously measure the impedance and resonant frequency of the attached sensor. The device accomplishes this task by regulating the oscillation amplitude in a closed-loop configuration to a constant level, while monitoring the energy dissipated by the resonator. By monitoring the amount of power injected into the resonator, the LDC1101 device can determine the value of R<sub>P</sub>. The device returns this value as a digital value which is proportional to R<sub>P</sub>. In addition, the LDC1101 device can also measure the oscillation frequency of the LC circuit, by counting the number of cycles of a reference frequency. The measured sensor frequency can be used to determine the inductance of the LC circuit.

#### 8.4.2.1 RPMIN and RPMAX

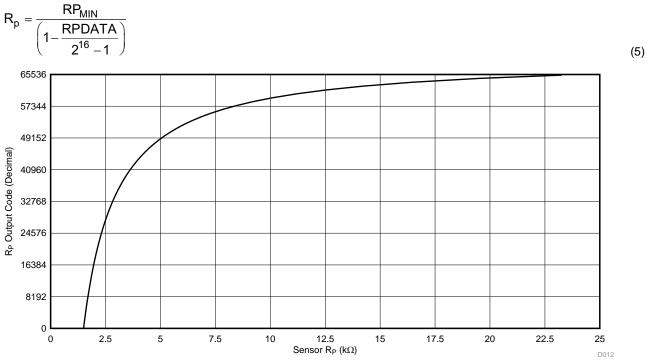

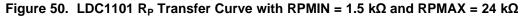

The variation of  $R_P$  in a given system is typically much smaller than maximum range of 1.25 k $\Omega$  to >90 k $\Omega$  supported by the LDC1101. To achieve better resolution for systems with smaller  $R_P$  ranges, the LDC1101 device offers a programmable  $R_P$  range.

The LDC1101 uses adjustable current drives to scale the  $R_P$  measurement range; by setting a tighter current range a higher accuracy  $R_P$  measurement can be performed. This functionality can be considered as a variable gain amplifier (VGA) front end to an ADC. The current ranges are configured in the RPMIN and RPMAX fields of register RP\_SET (address 0x01). Refer to LDC1101  $R_P$  Configuration for instructions to optimize these settings.

#### 8.4.2.2 Programmable Internal Time Constants

The LDC1101 utilizes internal programmable registers to configure time constants necessary for sensor oscillation. These internal time constants must be configured for  $R_P$  measurements. Refer to Setting Internal Time Constant 1 and Setting Internal Time Constant 2 for instructions on how to configure them for a given system.

#### 8.4.2.3 R<sub>P</sub>+L Mode Measurement Sample Rate

The LDC1101 provides an adjustable sample rate for the RP+L conversion, where longer conversion times have higher resolution. Refer to *RP+L Sample Rate Configuration with RESP\_TIME* for more details.

#### 8.4.3 High Resolution L (LHR) Measurement Mode

The High Resolution L measurement (LHR) subsystem provides a high-resolution inductance (L) measurement of up to 24 bits. This L measurement can be configured to provide a higher resolution measurement than the measurement returned from the RP+L subsystem. The LHR subsystem also provides a constant conversion time interval, whereas the RP+L conversion interval is a function of the sensor frequency. The LHR measurement runs asynchronously with respect to the RP+L measurement.

#### 8.4.4 Reference Count Setting

The LHR sample rate is set by the Reference Count (LHR\_RCOUNT) setting (registers 0x30 and 0x31). The LHR conversion resolution is proportional to the programmed RCOUNT value. With the maximum supported 16 MHz CLKIN input, the LDC1101 conversion interval can be set from 8.6  $\mu$ s to 87.38 ms in 1  $\mu$ s increments. Note that longer conversion intervals produce more accurate LHR measurements. Refer to *LHR Sample Rate Configuration with RCOUNT* for more details.

#### 8.4.5 L-Only Measurement Operation

The LDC1101 can disable the  $R_P$  measurement to perform a more stable L measurement. To enable this mode, set:

- ALT\_CONFIG.LOPTIMAL(register 0x05-bit0) = 1

- D\_CONFIG.DOK\_REPORT (register 0x0C-bit0) = 1

When this mode is used, R<sub>P</sub> measurement results are not valid.

#### 8.4.6 Minimum Sensor Frequency and Watchdog Setting

The LDC1101 can report an error condition if the sensor oscillation stops. Refer to *MIN\_FREQ and Watchdog Configuration* for information on the configuration of the watchdog.

#### 8.4.7 Low Power Modes

When continuous LDC conversions are not required, the LDC1101 supports two reduced power modes. In Sleep mode, the LDC1101 retains register settings and can quickly enter active mode for conversions. In Shutdown mode, power consumption is significantly lower, although the device configuration is not retained. While in either low power mode, the LDC1101 will not perform conversions.

#### 8.4.7.1 Shutdown Mode

Shutdown mode is the lowest power state for the LDC1101. Note that entering SD mode will reset all registers to their default state, and so the device must have its registers rewritten. To enter Shutdown, perform the following sequence:

- 1. Set ALT\_CONFIG.SHUTDOWN\_EN = 1 (register 0x05-bit[1]).

- 2. Stop toggling the CLKIN pin input and drive the CLKIN pin Low.

- 3. Set START\_CONFIG.FUNC\_MODE = b10 (register 0x0B:bits[1:0]). This register can be written while the LDC1101 is in active mode; on completion of the register write the LDC1101 will enter shutdown.

To exit Shutdown mode, resume toggling the clock input on the CLKIN pin; the LDC1101 will transition to Sleep mode with the default register values.

While in Shutdown mode, no conversions are performed. In addition, entering Shutdown mode will clear the status registers; if an error condition is present it will not be reported when the device exits Shutdown mode.

#### 8.4.7.2 Sleep Mode

Sleep mode is entered by setting START\_CONFIG.FUNC\_MODE =b01 (register 0x0B:bits[1:0]). While in this mode, the register contents are maintained. To exit Sleep mode and start active conversions, set START\_CONFIG.FUNC\_MODE = b00. While in Sleep mode the SPI interface is functional so that register reads and writes can be performed.

On power-up or exiting Shutdown mode, the LDC1101 will be in Sleep mode.

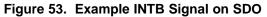

Configuring the LDC1101 must be done while the device is in Sleep mode. If a setting on the LDC1101 needs to be changed, return the device to Sleep mode, change the appropriate register, and then return the LDC1101 to conversion mode. The registers related to INTB reporting can be changed while the LDC1101 is in active mode. Refer to *INTB Reporting on SDO* for more details.

#### 8.4.8 Status Reporting

The LDC1101 provides 2 status registers, STATUS and LHR\_STATUS, to report on the device and sensor condition.

| NAME          | FIELD | FUNCTION                                                                                                                                                                                                                                                                                                                                  |

|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO_SENSOR_OSC | 7     | When the resonance impedance of the sensor, $R_P$ , drops below the programed $R_P$ _MIN, the sensor oscillation may stop. This condition is reported by STATUS:NO_SENSOR_OSC (register 0x20-bit7). This condition could occur when a target comes too close to the sensor or if RP_SET:RP_MIN (register 0x01-bits[2:0]) is set too high. |

| DRDYB         | 6     | RP+L Data Ready - reports completion of RP+L conversion results                                                                                                                                                                                                                                                                           |

| RP_HIN        | 5     |                                                                                                                                                                                                                                                                                                                                           |

| RP_HI_LON     | 4     | DD. I. threekeld - refer to Componente Exceptionality for dataile                                                                                                                                                                                                                                                                         |

| L_HIN         | 3     | RP+L threshold – refer to Comparator Functionality for details                                                                                                                                                                                                                                                                            |

| L_HI_LON      | 2     |                                                                                                                                                                                                                                                                                                                                           |

| POR_READ      | 0     | Device in Power-On Reset – device should only be configured when POR_READ = 0.                                                                                                                                                                                                                                                            |

#### Table 2. STATUS Fields

The LHR\_STATUS register (register 0x3B) reports on LHR functionality.

#### 8.4.9 Switch Functionality and INTB Reporting

The SDO pin can generate INTB, a signal which corresponds to device status. INTB can report conversion completion or provide a comparator output, in which the LDC conversion results are internally compared to programmable thresholds. Refer to *INTB Reporting on SDO* for details.

### 8.5 Programming

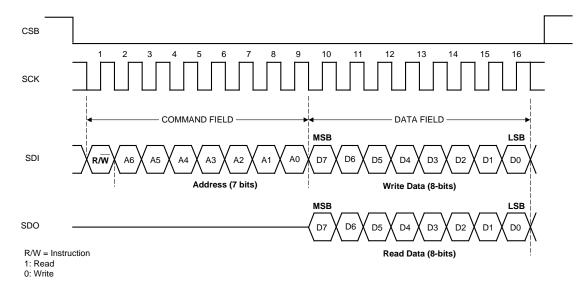

#### 8.5.1 SPI Programming

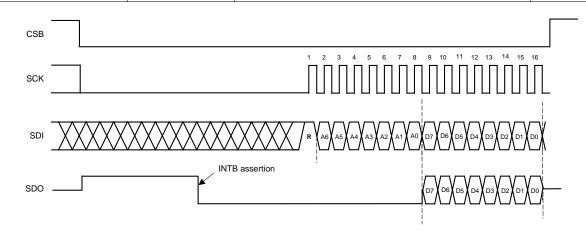

The LDC1101 uses SPI to configure the internal registers. It is necessary to configure the LDC1101 while in Sleep mode. If a setting on the LDC1101 needs to be changed, return the device to Sleep mode, change the appropriate register, and then return the LDC1101 to conversion mode. CSB must go low before accessing first address. If the number of SCLK pulses is less than 16, a register write command will not change the contents of the addressed register.

### **Programming (continued)**

The LDC1101 supports an extended SPI transaction, in which CSB is held low and sequential register addresses can be written or read. After the first register transaction, each additional 8 SCLK pulses will address the next register, reading or writing based on the initial R/W flag in the initial command. A register write command will take effect on the 8th clock pulse. Two or more registers can be programmed using this method. The register address must not increment above 0x3F.

Figure 13. Extended SPI Transaction

### 8.6 Register Maps

### Table 3. Register List

| ADDRESS | NAME            | DEFAULT<br>VALUE | DESCRIPTION                                                                                               |  |  |  |

|---------|-----------------|------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| 0x01    | RP_SET          | 0x07             | Configure R <sub>P</sub> Measurement Dynamic Range                                                        |  |  |  |

| 0x02    | TC1             | 0x90             | Configure Internal Time Constant 1                                                                        |  |  |  |

| 0x03    | TC2             | 0xA0             | Configure Internal Time Constant 2                                                                        |  |  |  |

| 0x04    | DIG_CONFIG      | 0x03             | Configure RP+L conversion interval                                                                        |  |  |  |

| 0x05    | ALT_CONFIG      | 0x00             | Configure additional device settings                                                                      |  |  |  |

| 0x06    | RP_THRESH_H_LSB | 0x00             | RP_THRESHOLD High Setting – bits 7:0. This register can be modified while the LDC1101 is in active mode.  |  |  |  |

| 0x07    | RP_THRESH_H_MSB | 0x00             | RP_THRESHOLD High Setting – bits 15:8. This register can be modified while the LDC1101 is in active mode. |  |  |  |

| 0x08    | RP_THRESH_L_LSB | 0x00             | RP_THRESHOLD Low Setting – bits 7:0. This register can be modified while the LDC1101 is in active mode.   |  |  |  |

| 0x09    | RP_THRESH_L_MSB | 0x00             | RP_THRESHOLD Low Setting – bits 15:8. This register can be modified while the LDC1101 is in active mode.  |  |  |  |

| 0x0A    | INTB_MODE       | 0x00             | Configure INTB reporting on SDO pin. This register can be modified while the LDC1101 is in active mode.   |  |  |  |

| 0x0B    | START_CONFIG    | 0x01             | Configure Power State                                                                                     |  |  |  |

| 0x0C    | D_CONF          | 0x00             | Sensor Amplitude Control Requirement                                                                      |  |  |  |

| 0x16    | L_THRESH_HI_LSB | 0x00             | L_THRESHOLD High Setting – bits 7:0. This register can be modified while the LDC1101 is in active mode.   |  |  |  |

| 0x17    | L_THRESH_HI_MSB | 0x00             | L_THRESHOLD High Setting – bits 15:8. This register can be modified while the LDC1101 is in active mode.  |  |  |  |

| 0x18    | L_THRESH_LO_LSB | 0x00             | L_THRESHOLD Low Setting – bits 7:0. This register can be modified while the LDC1101 is in active mode.    |  |  |  |

| 0x19    | L_THRESH_LO_MSB | 0x00             | L_THRESHOLD Low Setting – bits 15:8. This register can be modified while the LDC1101 is in active mode.   |  |  |  |

| 0x20    | STATUS          | 0x00             | Report RP+L measurement status                                                                            |  |  |  |

| 0x21    | RP_DATA_LSB     | 0x00             | R <sub>P</sub> Conversion Result Data Output - bits 7:0                                                   |  |  |  |

| 0x22    | RP_DATA_MSB     | 0x00             | R <sub>P</sub> Conversion Result Data Output - bits 15:8                                                  |  |  |  |

| 0x23    | L_DATA_LSB      | 0x00             | L Conversion Result Data Output - bits 7:0                                                                |  |  |  |

| 0x24    | L_DATA_MSB      | 0x00             | L Conversion Result Data Output - bits 15:8                                                               |  |  |  |

| 0x30    | LHR_RCOUNT_LSB  | 0x00             | High Resolution L Reference Count – bits 7:0                                                              |  |  |  |

| 0x31    | LHR_RCOUNT_MSB  | 0x00             | High Resolution L Reference Count – bits 15:8                                                             |  |  |  |

| 0x32    | LHR_OFFSET_LSB  | 0x00             | High Resolution L Offset – bits 7:0                                                                       |  |  |  |

| 0x33    | LHR_OFFSET_MSB  | 0x00             | High Resolution L Offset – bits 15:8                                                                      |  |  |  |

| 0x34    | LHR_CONFIG      | 0x00             | High Resolution L Configuration                                                                           |  |  |  |

| 0x38    | LHR_DATA_LSB    | 0x00             | High Resolution L Conversion Result Data output - bits 7:0                                                |  |  |  |

| 0x39    | LHR_DATA_MID    | 0x00             | High Resolution L Conversion Result Data output - bits 15:8                                               |  |  |  |

| 0x3A    | LHR_DATA_MSB    | 0x00             | High Resolution L Conversion Result Data output - bits 23:16                                              |  |  |  |

| 0x3B    | LHR_STATUS      | 0x00             | High Resolution L Measurement Status                                                                      |  |  |  |

| 0x3E    | RID             | 0x02             | Device RID value                                                                                          |  |  |  |

| 0x3F    | CHIP_ID         | 0xD4             | Device ID value                                                                                           |  |  |  |

#### 8.6.1 Individual Register Listings

Fields indicated with Reserved must be written only with indicated values. Improper device operation may occur otherwise. The R/W column indicates the Read-Write status of the corresponding field. A 'R/W' entry indicates read and write capability, a 'R' indicates read-only, and a 'W' indicates write-only.

### 8.6.2 Register RP\_SET (address = 0x01) [reset = 0x07]

### Figure 14. Register RP\_SET

| 7         | 6 | 5      | 4 | 3        | 2 | 1      | 0 |

|-----------|---|--------|---|----------|---|--------|---|

| RPMAX_DIS |   | RP_MAX |   | RESERVED |   | RP_MIN |   |

| R/W       |   | R/W    |   | R/W      |   | R/W    |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 4. Register RP\_SET Field Descriptions

| Bit | Field     | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|-----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RPMAX_DIS | R/W  | 0     | RP_MAX Disable                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |           |      |       | This setting improves the $R_P$ measurement accuracy for very high Q coils by driving 0A as the $R_{PMAX}$ current drive.                                                                                                                                                                                                                                                                                                                                  |

|     |           |      |       | b0: Programmed RP_MAX is driven <b>(default value)</b><br>b1: RP_MAX current is ignored; current drive is off.                                                                                                                                                                                                                                                                                                                                             |

| 6:4 | RP_MAX    | R/W  | b000  | RP_MAX Setting                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |           |      |       | Set the maximum input dynamic range for the sensor $R_P$ measurement. The programmed RP_MIN setting must not exceed the programmed RP_MAX setting.<br>b000: RPMAX = 96 k $\Omega$ (default value)<br>b001: RPMAX = 48 k $\Omega$<br>b010: RPMAX = 24 k $\Omega$<br>b010: RPMAX = 24 k $\Omega$<br>b011: RPMAX = 12 k $\Omega$<br>b100: RPMAX = 6 k $\Omega$<br>b101: RPMAX = 3 k $\Omega$<br>b110: RPMAX = 1.5 k $\Omega$<br>b111: RPMAX = 0.75 k $\Omega$ |

| 3   | RESERVED  | R/W  | 0     | Reserved. Set to 0                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2:0 | RP_MIN    | R/W  | b111  | RP_MIN Setting                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |           |      |       | Set the minimum input dynamic range for the sensor $R_P$ measurement. The programmed RP_MIN setting must not exceed the programmed RP_MAX setting.<br>b000: RPMIN = 96 k $\Omega$<br>b001: RPMIN = 48 k $\Omega$<br>b010: RPMIN = 24 k $\Omega$<br>b011: RPMIN = 12 k $\Omega$<br>b100: RPMIN = 12 k $\Omega$<br>b100: RPMIN = 6 k $\Omega$<br>b101: RPMIN = 3 k $\Omega$<br>b110: RPMIN = 1.5 k $\Omega$<br>b111: RPMIN = 0.75 k $\Omega$ (default value) |

# 8.6.3 Register TC1 (address = 0x02) [reset = 0x90]

www.ti.com

### Figure 15. Register TC1

| 7  | 6 | 5        | 4 | 3 | 2   | 1 | 0 |

|----|---|----------|---|---|-----|---|---|

| С  | 1 | RESERVED |   |   | R1  |   |   |

| R/ | W | R/W      |   |   | R/W |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 5. Register TC1 Field Descriptions

| Bit | Field    | Туре | Reset  | Description                                                                                                                                                                                                                                    |

|-----|----------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | C1       | R/W  | b10    | Internal Time Constant 1 Capacitance                                                                                                                                                                                                           |

|     |          |      |        | This sets the capacitive component used to configure internal time constant 1.<br>Refer to Setting Internal Time Constant 1 for more details.<br>b00: C1 = 0.75 pF<br>b01: C1 = 1.5 pF<br>b10: C1 = 3.0 pF (default value)<br>b11: C1 = 6.0 pF |

| 5   | RESERVED | R/W  | 0      | Reserved. Set to 0                                                                                                                                                                                                                             |

| 4:0 | R1       | R/W  | b1'000 | Internal Time Constant 1 Resistance                                                                                                                                                                                                            |

|     |          |      | 0      | This sets the resistive component used to configure internal time constant 1. Refer to <i>Setting Internal Time Constant 1</i> for configuration details.                                                                                      |

|     |          |      |        | R1(Ω) = -12.77 kΩ × R1 + 417 kΩ                                                                                                                                                                                                                |

|     |          |      |        | Valid Values: [b0'0000:b1'1111]                                                                                                                                                                                                                |

|     |          |      |        | b0'0000: R <sub>1</sub> = 417 kΩ<br>b1'0000: R <sub>1</sub> = 212.7kΩ <b>(default value)</b>                                                                                                                                                   |

|     |          |      |        | b1'0000. $R_1 = 21.2.7 \text{ km}$ (default value)<br>b1'1111: $R_1 = 21.1 \text{ km}$                                                                                                                                                         |

### 8.6.4 Register TC2 (address = 0x03) [reset = 0xA0]

### Figure 16. Register TC2

| 7 | 6   | 5 | 4 | 3  | 2 | 1 | 0 |

|---|-----|---|---|----|---|---|---|

|   | C2  |   |   | R  | 2 |   |   |

| F | R/W |   |   | R/ |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 6. Register TC2 Field Descriptions

| Bit | Field | Туре | Reset   | Description                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | C2    | R/W  | b10     | Internal Time Constant 2 Capacitance                                                                                                                                                                                                                                                                                                                                 |

|     |       |      |         | This sets the capacitive component used to configure internal time constant 2.<br>Refer to Setting Internal Time Constant 2 for configuration details.<br>b00: C2 = 3 pF<br>b01: C2 = 6 pF<br>b10: C2 = 12 pF (default value)<br>b11: C2 = 24 pF                                                                                                                     |

| 5:0 | R2    | R/W  | b10'000 | Internal Time Constant 2 Resistance                                                                                                                                                                                                                                                                                                                                  |

|     |       |      | 0       | This sets the resistive component used to configure internal time constant 2.<br>Refer to Setting Internal Time Constant 2 for details.<br>$R_2(\Omega) = -12.77 \ k\Omega \times R_2 + 835 \ k\Omega$<br>Valid Values: [b00'0000:b11'1111]<br>b00'0000: $R_2 = 835k\Omega$<br>b10'0000: $R_2 = 426.4 \ k\Omega$ (default value)<br>b11'1111: $R_2 = 30.5 \ k\Omega$ |

### 8.6.5 Register DIG\_CONF (address = 0x04) [reset = 0x03]

### Figure 17. Register DIG\_CONF

| 7 | 6        | 5 | 4 | 3 | 2 | 1         | 0 |

|---|----------|---|---|---|---|-----------|---|

|   | MIN_FREQ |   |   |   |   | RESP_TIME |   |

|   | <br>R/W  |   |   |   |   |           |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 7. Register DIG\_CONF Field Descriptions

| Bit | Field     | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                            |

|-----|-----------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | MIN_FREQ  | R/W  | 0x0   | Sensor Minimum Frequency                                                                                                                                                                                                                                                                                                                               |

|     |           |      |       | Configure this register based on the lowest possible sensor frequency. This is typically when the target is providing minimum interaction with the sensor, although with some steel and ferrite targets, the minimum sensor frequency occurs with maximum target interaction.                                                                          |

|     |           |      |       | This setting should include any additional effects which reduce the sensor frequency, including temperature shifts and sensor capacitor variation.                                                                                                                                                                                                     |

|     |           |      |       | $MIN\_FREQ = 16 - (8 MHz \div f_{SENSORMIN})$                                                                                                                                                                                                                                                                                                          |

|     |           |      |       | b0000: f <sub>SENSORMIN</sub> = 500 kHz <b>(default value)</b><br>b1111: f <sub>SENSORMIN</sub> = 8 MHz                                                                                                                                                                                                                                                |

| 3   | RESERVED  | R/W  | 0     | Reserved. Set to 0                                                                                                                                                                                                                                                                                                                                     |

| 2:0 | RESP_TIME | R/W  | b011  | Measurement Response Time Setting                                                                                                                                                                                                                                                                                                                      |

|     |           |      |       | Sets the Response Time, which is the number of sensor periods used per conversion. This setting applies to the R <sub>P</sub> and Standard Resolution L measurement, but not the High Resolution L measurement. This corresponds to the actual conversion time by:<br>Conversion Time (s) = $\frac{\text{Re sponse Time}}{3 \times f_{\text{SENSOR}}}$ |

|     |           |      |       | b000: Reserved (do not use)<br>b001: Reserved (do not use)<br>b010: Response Time = 192<br>b011: Response Time = 384 <b>(default value)</b><br>b100: Response Time = 768                                                                                                                                                                               |

|     |           |      |       | b101: Response Time = 1536                                                                                                                                                                                                                                                                                                                             |

|     |           |      |       | b110: Response Time = 3072                                                                                                                                                                                                                                                                                                                             |

|     |           |      |       | b111: Response Time = 6144                                                                                                                                                                                                                                                                                                                             |

### 8.6.6 Register ALT\_CONFIG (address = 0x05) [reset = 0x00]

### Figure 18. Register ALT\_CONFIG

| 7 | 6 | 5    | 4 | 3           | 2        | 1   | 0 |

|---|---|------|---|-------------|----------|-----|---|

|   |   | RESE |   | SHUTDOWN_EN | LOPTIMAL |     |   |

|   |   | R/\  |   |             | R/W      | R/W |   |

| Table 8. Register ALT | _CONFIG Field Descriptions |

|-----------------------|----------------------------|

|-----------------------|----------------------------|

| Bit | Field       | Туре | Reset    | Description                                                                                                                                                                                                         |

|-----|-------------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | RESERVED    | R/W  | b00'0000 | Reserved. Set to b00'0000.                                                                                                                                                                                          |

| 1   | SHUTDOWN_EN | R/W  | 0        | Shutdown Enable                                                                                                                                                                                                     |

|     |             |      |          | Enables shutdown mode of operation. If SHUTDOWN_EN is not set to 1, then SHUTDOWN (Address 0x0B:[1]) will not have any effect. b0: Shutdown not enabled <b>(default value).</b> b1: Shutdown functionality enabled. |

TEXAS INSTRUMENTS

www.ti.com

| Bit | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | LOPTIMAL | R/W  | 0     | Optimize for L Measurements                                                                                                                                                                                                                                                                                                                                                                                   |

|     |          |      |       | Optimize sensor drive signal for L measurements (for both High-Res L and L measurement). When LOPTIMAL is enabled, R <sub>P</sub> measurements will not be completed. It is also necessary to set DOK_REPORT=1 when this mode is enabled.<br>b0: L optimal disabled; both RP+L/LHR measurements (default value).<br>b1: Only perform LHR and/or L-only measurements. R <sub>P</sub> measurements are invalid. |

### Table 8. Register ALT\_CONFIG Field Descriptions (continued)

### 8.6.7 Register RP\_THRESH\_HI\_LSB (address = 0x06) [reset = 0x00]

This register can be modified while the LDC1101 is in active mode.

### Figure 19. Register RP\_THRESH\_HI\_LSB

| 7 | 6 | 5 | 4       | 3         | 2 | 1 | 0 |

|---|---|---|---------|-----------|---|---|---|

|   |   |   | RP_THRE | SH_HI_LSB |   |   |   |

|   |   |   | R       | 2/W       |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 9. Register RP\_THRESH\_HI\_LSB Field Descriptions

| Bit | Field            | Туре | Reset | Description                                                                                                                                                                                                                    |

|-----|------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | RP_THRESH_HI_LSB | R/W  | 0x00  | R <sub>P</sub> High Threshold LSB Setting                                                                                                                                                                                      |

|     |                  |      |       | Combine with value in Register RP_THRESH_HI_MSB (Address 0x07) to set the upper $R_P$ conversion threshold:                                                                                                                    |

|     |                  |      |       | RP_THRESH_HI = RP_THRESH_HI[15:8] × 256 + RP_THRESH_HI[7:0]                                                                                                                                                                    |

|     |                  |      |       | If RP_DATA conversion result is greater than the RP_THRESH_HI, RP_TH_I will be asserted.                                                                                                                                       |

|     |                  |      |       | Note that RP_THRESH_HI_LSB is buffered and will not change the device configuration until a write to RP_TRESH_HI_MSB is performed. Note that both registers 0x06 and 0x07 must be written to change the value of RP_THRESH_HI. |

|     |                  |      |       | 0x00: default value                                                                                                                                                                                                            |

### 8.6.8 Register RP\_THRESH\_HI\_MSB (address = 0x07) [reset = 0x00]

This register can be modified while the LDC1101 is in active mode.

#### Figure 20. Register RP\_THRESH\_HI\_MSB

| 7 | 6                | 5 | 4 | 3 | 2 | 1 | 0 |

|---|------------------|---|---|---|---|---|---|

|   | RP_THRESH_HI_MSB |   |   |   |   |   |   |

|   | R/W              |   |   |   |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 10. Register RP\_THRESH\_HI\_MSB Field Descriptions

| Bit | Field            | Туре | Reset | Description                                                                                                                              |

|-----|------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | RP_THRESH_HI_MSB | R/W  | 0x00  | R <sub>P</sub> High Threshold MSB Setting                                                                                                |

|     |                  |      |       | Combine with value in Register RP_THRESH_HI_LSB (Address 0x06) to set the upper R <sub>P</sub> conversion threshold. 0x00: default value |

### 8.6.9 Register RP\_THRESH\_LO\_LSB (address = 0x08) [reset = 0x00]

This register can be modified while the LDC1101 is in active mode.

#### Figure 21. Register RP\_THRESH\_LO\_LSB

| 7 | 6 | 5 | 4        | 3         | 2 | 1 | 0 |

|---|---|---|----------|-----------|---|---|---|

|   |   |   | RP_THRES | SH_LO_LSB |   |   |   |

|   |   |   | R        | /W        |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 11. Register RP\_THRESH\_LO\_LSB Field Descriptions

| Bit | Field             | Туре | Reset | Description                                                                                                                                                                                                                         |

|-----|-------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | RP_THRESH_LO[7:0] | R/W  | 0x00  | R <sub>P</sub> Low Threshold LSB Setting                                                                                                                                                                                            |

|     |                   |      |       | Combine with value in Register RP_THRESH_LO_MSB (Address 0x09) to set the lower R <sub>P</sub> conversion threshold:<br>RP_THRESH_LO = RP_THRESH_LO[15:8] ×256 +<br>RP_THRESH_LO[7:0]                                               |

|     |                   |      |       | If RP_DATA conversion result is less than the RP_THRESH_LO,<br>RP_HI_LON will be asserted. Note that RP_THRESH_LO_LSB is<br>buffered and will not change the device configuration until a write to<br>RP_TRESH_LO_MSB is performed. |

|     |                   |      |       | Note that both registers 0x08 and 0x09 must be written to change the value of RP_THRESH_LO. 0x00: default value                                                                                                                     |

#### 8.6.10 Register RP\_THRESH\_LO\_MSB (address = 0x09) [reset = 0x00]

This register can be modified while the LDC1101 is in active mode

#### Figure 22. Register RP\_THRESH\_LO\_MSB

| 7 | 6 | 5 | 4        | 3         | 2 | 1 | 0 |

|---|---|---|----------|-----------|---|---|---|

|   |   |   | RP_THRES | SH_LO_MSB |   |   |   |

|   |   |   | R        | /W        |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 12. Register RP\_THRESH\_LO\_MSB Field Descriptions

| Bit | Field              | Туре | Reset | Description                                                                                                                     |

|-----|--------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------|