## Ultra-low power, high performance, sub-1GHz transceiver

## Features

- Frequency bands:

- 430-470 MHz (S2-LPQTR)

- 470-512 MHz (S2-LPCBQTR)

- 860-940 MHz (S2-LPQTR)

- Modulation schemes:

- 2(G)FSK, 4(G)FSK

- OOK, ASK

- Air data rate from 0.1 to 500 kbps

- Ultra-low power consumption:

- 7 mA RX

- 10 mA TX @ +10 dBm

- Excellent performance of receiver sensitivity: down to -130 dBm

- Excellent receiver selectivity and blocking

- Programmable RF output power up to +16 dBm

- Programmable RX digital filter

- Programmable channel spacing

- · Fast start-up and frequency synthesizer settling time

- Automatic frequency offset compensation, AGC and symbol timing recovery

- More than 145 dB RF link budget

- Battery indicator and low battery detector

- RX and TX 128 bytes FIFO buffers

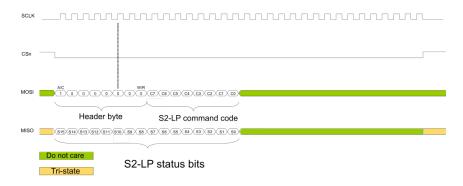

- 4-wire SPI interface

- Automatic packet acknowledgment and retransmission

- Embedded timeout protocol engine

- Excellent receiver selectivity (> 80 dB @ 2 MHz)

- ST companion integrated balun/filter chips are available

- Antenna diversity algorithm

- Fully integrated ultra-low power RC oscillator

- · Wake-up driven by internal timer or external event

- Digital real time RSSI

- Flexible packet length with dynamic payload length

- · Programmable preamble and SYNC word quality filtering and detection

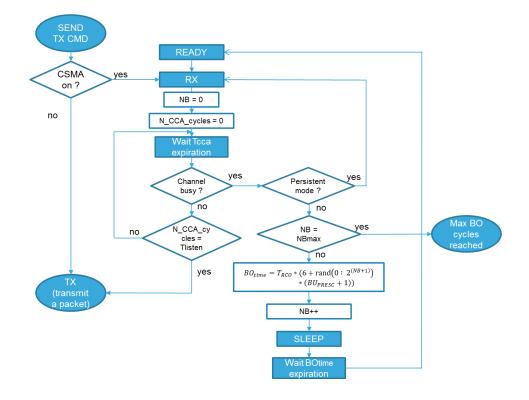

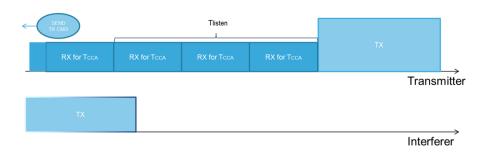

- Embedded CSMA/CA engine based on listen-before-talk systems

- IEEE 802.15.4g hardware packet support with whitening, FEC, CRC and dual SYNC word detection

- Wireless M-BUS supported

- Enables operations in the SIGFOX™ networks

- Suitable to build systems targeting:

- Europe: ETSI EN 300 220, category 1.5 natively compliant, ETSI EN 303 131

- US: FCC part 15 and part 90

- Japan: ARIB STD T67, T108

Maturity status link S2-LP

- China: SRRC

- Operating temperature range: -40 °C to +105 °C

## **Applications**

- Sensors to Cloud

- Smart metering

- Home energy management systems

- Wireless alarm systems

- Smart home

- Building automation

- Industrial monitoring and control

- Smart lighting systems

## 1 Description

The S2-LP is a high performance ultra-low power RF transceiver, intended for RF wireless applications in the sub-1 GHz band. It is designed to operate in both the license-free ISM and SRD frequency bands at 433, 512, 868 and 920 MHz, but can also be programmed to operate at other additional frequencies in the 430-470 MHz, 470-512 MHz, 860-940 MHz bands.

The S2-LP supports different modulation schemes: 2(G)FSK, 4(G)FSK, OOK and ASK. The air data rate is programmable from 0.1 to 500 kbps.

The S2-LP can be used in systems with channel spacing down to 1 kHz enabling the narrow band operations.

The S2-LP shows an RF link budget higher than 140 dB for long communication ranges and meets the regulatory requirements applicable in territories worldwide, including Europe, Japan, China and the USA.

## 2 Detailed functional description

57/

The S2-LP integrates a configurable baseband modem with proprietary fully programmable packet format allowing also:

- IEEE 802.15.4g applications

- The hardware packet supports whitening, CRC, FEC and dual SYNC word detection.

- Wireless M-Bus applications

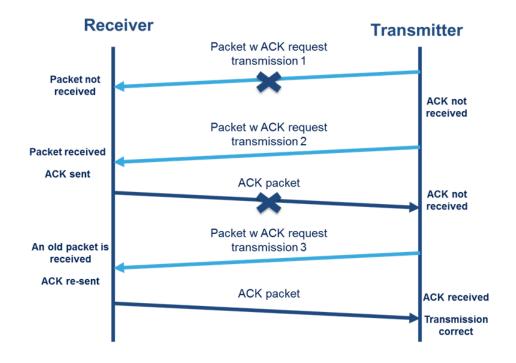

In order to reduce the overall system power consumption and increase the communication reliability, the S2-LP provides an embedded programmable automatic packet acknowledgment, automatic packet retransmission, CSMA/CA engine, low duty cycle protocol, RX sniff mode and timeout protocol.

The S2-LP fully supports antenna diversity with an integrated antenna switching control algorithm.

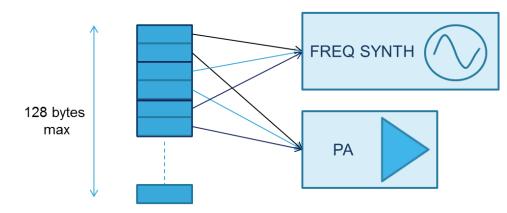

Transmitted/received data bytes are buffered in two different 128 bytes FIFOs (TX FIFO and RX FIFO), accessible via SPI interface for host processing.

In addition, the reduced number of external components enables a cost effective solution permitting a compact PCB footprint.

The S2-LP targets volume applications like:

- Sensors to Cloud

- Smart metering

- Home energy management systems

- Wireless alarm systems

- Smart home

- Building automation

- Industrial monitoring and control

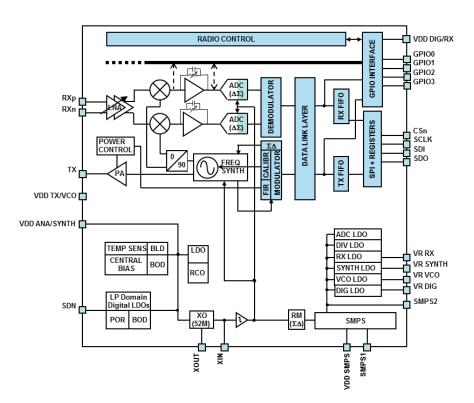

### Figure 1. Simplified S2-LP block diagram

The receiver architecture is low-IF conversion, the received RF signal is amplified by a two-stage low-noise amplifier (LNA) and down-converted in quadrature (I and Q) to the intermediate frequency (IF). LNA and IF amplifiers make up the RX front-end (RXFE) and have programmable gain. At IF, the ADCs digitalize the I/Q signals. The demodulated data go to an external MCU either through the 128-byte RX FIFO, readable via SPI, or directly using a programmable GPIO pin.

The transmitter part of the S2-LP is based on direct synthesis of the RF frequency. The power amplifier (PA) input is the LO generated by the RF synthesizer, while the output level can be configured between -30 dBm and +14 dBm (+16 dBm in boost mode), at antenna level with 0.5 dB steps.

The data to be transmitted can be provided by an external MCU either through the 128-byte TX FIFO writable via SPI, or directly using a programmable GPIO pin. The S2-LP supports frequency hopping, TX/RX and antenna diversity switch control, extending the link range and improving performance.

The S2-LP has a very efficient power management (PM) system. An integrated switched mode power supply (SMPS) regulator allows operation from a battery voltage ranging from +1.8 V to +3.6 V, and with power conversion efficiency of 90%.

A crystal must be connected between XIN and XOUT. It is digitally configurable to operate with different crystals. As an alternative, an external clock signal can be used to feed XIN for proper operation. The S2-LP also has an integrated low-power RC oscillator, generating the 34.7 kHz signal used as a clock for the slowest timeouts.

A standard 4-pin SPI bus is used to communicate with the external MCU. Four configurable general purpose I/Os are available.

# 3 Typical application diagram and pin description

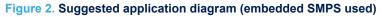

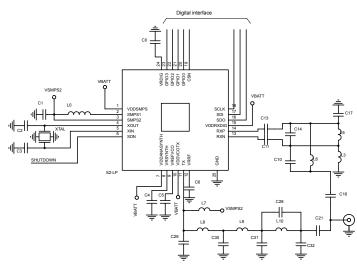

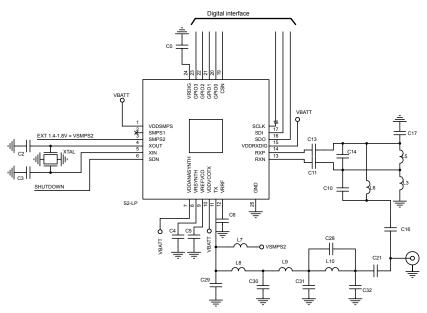

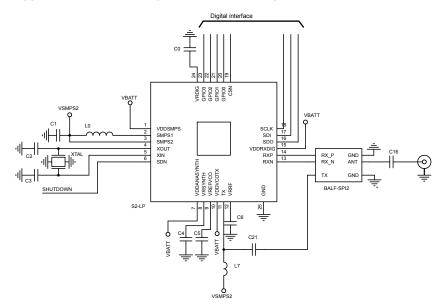

This section describes three different application diagrams for the S2-LP. Two main configurations are available:

- HPM (high performance mode) configuration

- LPM (low power mode) configuration

In the LPM operating mode the LDOs are bypassed and the SMPS provides the regulator voltage at 1.2 V. Note that in LPM the PA is supplied from SMPS at 1.2 V (instead of 1.5 V as in HPM), so the max. output power is lower than HPM. The figure below shows the suggested configuration with discrete matching network and SMPS-ON.

Figure 3. Suggested application diagram (embedded SMPS not used) shows the suggested configuration with discrete matching network and SMPS-OFF mode, it allows the sensitivity to be improved by the power consumption rise.

### Figure 4. Suggested application diagram HPM/LPM (integrated balun, embedded SMPS used)

### Table 1. Description of the external components of the typical application diagrams

| Components         | HPM/LPM d | iscrete balun | HPM/LPM          | Description                                                                 |

|--------------------|-----------|---------------|------------------|-----------------------------------------------------------------------------|

|                    | SMPS ON   | SMPS OFF      | integrated balun |                                                                             |

| C0                 | Х         | Х             | Х                | Decoupling capacitor for on-chip voltage regulator to<br>digital part       |

| C1                 | Х         | -             | Х                | SMPS LC filter capacitors                                                   |

| C2, C3             | Х         | Х             | Х                | Crystal loading capacitors                                                  |

| C4                 | Х         | Х             | Х                | Decoupling capacitor for on-chip voltage regulator to synthesizer (LF part) |

| C5                 | Х         | Х             | Х                | Decoupling capacitor for band-gap voltage reference<br>of VCO regulator     |

| C6                 | Х         | Х             | Х                | Decoupling capacitor for on-chip voltage regulator to LNA-MIXER             |

| C29, C30, C31, C32 | Х         | Х             |                  | TX LC filter/matching capacitors                                            |

| C11, C13           | Х         | Х             |                  | DC blocking capacitors                                                      |

| C16, C21           | Х         | Х             | Х                |                                                                             |

| C10, C14, C17      | Х         | Х             |                  | RF balun/matching capacitors                                                |

| LO                 | Х         | -             | Х                | SMPS LC filter inductor                                                     |

| L7                 | Х         | Х             | Х                | RF choke inductor or resonating inductor (upon RF network topology)         |

| L8, L9, L10        | Х         | Х             |                  | TX LC filter/matching inductors                                             |

| L3, L5, L6         | Х         | Х             |                  | RX balun/matching inductors                                                 |

| XTAL               | Х         | Х             | х                | Crystal                                                                     |

57

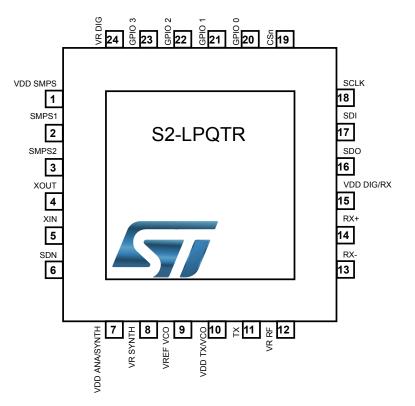

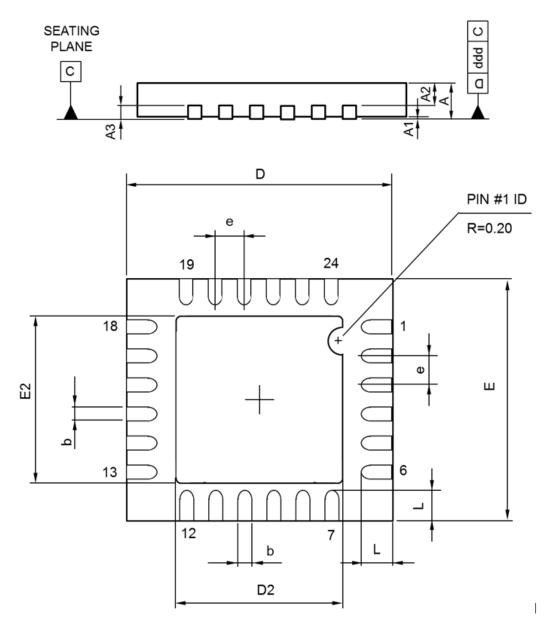

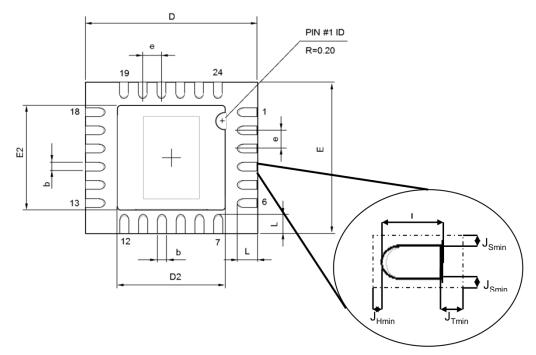

## 3.1 Pin diagram

57

## Figure 5. Pin diagram, QFN24 (4x4 mm) package

## 3.2 Pin description

### Table 2. Pinout

| Number | Pin name          | Pin type      | Description                                                                                                                                                                                                                                                                                            |

|--------|-------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VDD SMPS          | Power         | 1.8 V to 3.6 V analog power supply for SMPS only.                                                                                                                                                                                                                                                      |

| 2      | SMPS1             | Analog out    | 1.1 V to 1.8 V SMPS regulator output to be externally filtered                                                                                                                                                                                                                                         |

| 3      | SMPS2             | Analog in     | 1.1 V to 1.8 V SMPS voltage input after LC filtering applied to SMPS1 output                                                                                                                                                                                                                           |

| 4      | XOUT              | Analog out    | Crystal oscillator output. Connect to an external crystal or leave floating if driving the XIN pin with an external clock source                                                                                                                                                                       |

| 5      | XIN               | Analog in     | Crystal oscillator input. Connect to an external crystal or to an external clock source. If using an external clock source, DC coupling with a minimum 0.2 VDC level is recommended and minimum AC amplitude of 400 mVpp (however, the instantaneous level at input cannot exceed the 0 – 1.4 V range) |

| 6      | SDN               | Digital in    | Shutdown input pin. SDN should be = '0' in all modes, except shutdown mode                                                                                                                                                                                                                             |

| 7      | VDD ANA/<br>SYNTH | Power         | 1.8 V to 3.6 V power                                                                                                                                                                                                                                                                                   |

| 8      | VR SYNTH          | Analog in/out | 1.2 V SYNTH-LDO output for decoupling                                                                                                                                                                                                                                                                  |

| 9      | VREF VCO          | Analog out    | 1.2 V VCO-LDO for decoupling                                                                                                                                                                                                                                                                           |

| 10     | VDD VCO/TX        | Power         | 1.8 V to 3.6 V power supply                                                                                                                                                                                                                                                                            |

| 11     | ТХ                | RF output     | RF output signal                                                                                                                                                                                                                                                                                       |

| Number | Pin name   | Pin type      | Description                                                                     |  |  |  |  |

|--------|------------|---------------|---------------------------------------------------------------------------------|--|--|--|--|

| 12     | VR RF      | Analog in/out | 1.2 V RX-LDO output for decoupling                                              |  |  |  |  |

| 13     | RXn        | RF in         | Differential RF input signals for the LNA                                       |  |  |  |  |

| 14     | RXp        | RF in         |                                                                                 |  |  |  |  |

| 15     | VDD RX/DIG | Power         | 1.8 V to 3.6 V power supply                                                     |  |  |  |  |

| 16     | SDO        | Digital out   | SPI slave data output                                                           |  |  |  |  |

| 17     | SDI        | Digital in    | SPI slave data input                                                            |  |  |  |  |

| 18     | SCLK       | Digital in    | SPI slave clock input                                                           |  |  |  |  |

| 19     | CSn        | Digital in    | SPI chip select                                                                 |  |  |  |  |

| 20     | GPIO0      | Digital I/O   | General purpose I/O that may be configured through the SPI registers to perform |  |  |  |  |

| 21     | GPIO1      | Digital I/O   | various functions                                                               |  |  |  |  |

| 22     | GPIO2      | Digital I/O   |                                                                                 |  |  |  |  |

| 23     | GPIO3      | Digital I/O   |                                                                                 |  |  |  |  |

| 24     | VR DIG     | Analog in/out | 1.2 V digital power supply output for decoupling                                |  |  |  |  |

| 25     | GND        | Ground        | Exposed pin connected to the ground of the application board                    |  |  |  |  |

## 4 Specifications

## 4.1 Absolute maximum ratings

Absolute maximum ratings are those values above which damage to the device may occur. Functional operation under these conditions is not implied. All voltages refer to GND.

| Parameter                         | Min. | Тур. | Max. | Unit |

|-----------------------------------|------|------|------|------|

| Supply and SMPS pins              | -0.3 |      | +3.9 | V    |

| DC voltage on VREG pins           | -0.3 |      | +3.9 |      |

| DC voltage on digital input pins  | -0.3 |      | +3.9 |      |

| DC voltage on digital output pins | -0.3 |      | +3.9 |      |

| DC voltage on ground pins         | -0.3 |      | +3.9 |      |

| DC voltage on analog pins         | -0.3 |      | +1.8 |      |

| DC voltage on TX pin              | -0.3 |      | +3.9 |      |

| Storage temperature range         | -40  |      | +125 | °C   |

| VESD-HBM                          | -500 |      | +500 | V    |

### Table 3. Absolute maximum ratings

## 4.2 Operating range

### Table 4. Operating range

| Parameter                                            | Min.               | Тур. | Max. | Unit |

|------------------------------------------------------|--------------------|------|------|------|

| Operating battery supply voltage (V <sub>BAT</sub> ) | 1.8 <sup>(1)</sup> | 3.0  | 3.6  | V    |

| Operating ambient temperature range                  | -40                | 25   | +105 | °C   |

1. 2 V when the device works in boost mode with SMPS ON.

## 4.3 Thermal properties

### Table 5. Thermal data

| Parameter                           | QFN24 | Unit |

|-------------------------------------|-------|------|

| Thermal resistance junction-ambient | 66    | °C/W |

### 4.4 Power consumption

Characteristics measured over recommended operating conditions unless otherwise specified. Typical values are referred to 25 °C temperature,  $V_{BAT}$  = 3.0 V. All performance is referred to the STEVAL-FKI433V1 or STEVAL-FKI868V1 with a 50 Ohm antenna connector.

#### Table 6. Low-power state power consumption

| Parameter      | Test conditions        | Min. | Тур. | Max. | Unit |

|----------------|------------------------|------|------|------|------|

| Supply current | Shutdown               | -    | 2.5  | -    | nA   |

|                | Standby                |      | 500  |      |      |

|                | Sleep                  |      | 700  |      |      |

|                | Sleep (FIFOs retained) |      | 0.95 |      | μA   |

|                | Ready                  |      | 420  |      |      |

#### Table 7. Power consumption in reception TA = 25 °C, VDD = 3.0 V, fc = 868 MHz

| Parameter      | Test conditions                             | Min. | HPM typ. | LPM typ. | Max. | Unit |

|----------------|---------------------------------------------|------|----------|----------|------|------|

| Supply current | RX @ sensitivity level                      |      | 8.6      | 7.2      |      | mA   |

|                | RX in sniff mode @ 1.2 kbps (1)             |      | 0.9      |          |      |      |

|                | RX in sniff mode @ 38.4 kbps <sup>(2)</sup> |      | 0.8      |          |      |      |

|                | RX in LDC mode @ 1.2 kbps $^{(3)}$          | -    | 21       |          |      | μA   |

|                | RX in LDC mode @ 38.4 kbps <sup>(4)</sup>   |      | 3        |          |      |      |

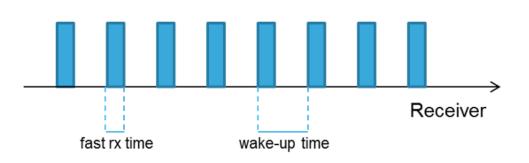

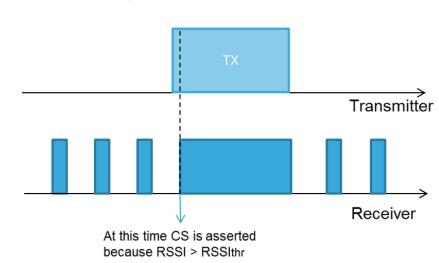

1. Using 2-FSK, FREQDEV = 2.4 kHz, DR=1.2 kbps, 4 bytes preamble and 8 kHz ch. filter. Where the receiver wakes up at regular intervals to look for an incoming packet.

2. Using 2-FSK, FREQDEV = 20 kHz, DR=38.4 kbps, 24 bytes preamble and 100 kHz ch. filter. Where the receiver wakes up at regular intervals to look for an incoming packet.

3. Check for data packet every 1 second in LDC mode. 2-FSK, FREQDEV = 1.2 kHz DEV and 8 kHz ch. filter, DR=1.2 kbps, internal RC oscillator used as sleep timer. Sniff timer enabled.

4. Check for data packet every 1 second in LDC mode. 2-FSK, FREQDEV = 20 kHz, DR=38.4 kbps and 100 kHz ch. filter, internal 34.6 kHz RC oscillator used as sleep timer. Sniff timer enabled.

#### Table 8. Power consumption in transmission fc= 915 MHz

| Parameter      | Test conditions               | Min. | Тур. | Max. | Unit |

|----------------|-------------------------------|------|------|------|------|

| Supply current | TX CW @ 14 dBm                |      | 20.6 |      | mA   |

|                | TX CW @ 10 dBm <sup>(1)</sup> |      | 11.7 |      |      |

|                | TX CW @ 16 dBm in Boost (2)   |      | 27   |      |      |

1. SMPS output voltage 1.2 V, LDOs disable.

2. SMPS output voltage 1.8 V.

#### Table 9. Power consumption in transmission fc= 868 MHz

| Parameter      | Test conditions               | Min. | Тур. | Max. | Unit |

|----------------|-------------------------------|------|------|------|------|

| Supply current | TX CW @ 14 dBm                |      | 20   |      | mA   |

|                | TX CW @ 10 dBm <sup>(1)</sup> |      | 11   |      |      |

|                | TX CW @ 16 dBm in Boost (2)   |      | 27   |      |      |

1. SMPS output voltage 1.2 V, LDOs disable.

2. SMPS output voltage 1.8 V.

| Parameter      | Test conditions | Min. | Тур. | Max. | Unit |

|----------------|-----------------|------|------|------|------|

| Supply current | TX CW @ 14 dBm  |      | 19   |      | mA   |

|                | TX CW @ 10 dBm  |      | 11.5 |      |      |

### Table 10. Power consumption in transmission fc= 434 MHz

### Table 11. Power consumption in transmission f<sub>c</sub> = 510 MHz

| Parameter      | Test conditions               | Min. | Тур. | Max. | Unit |

|----------------|-------------------------------|------|------|------|------|

| Supply current | TX CW @ 14 dBm                |      | 19   |      | mA   |

|                | TX CW @ 10 dBm <sup>(1)</sup> |      | 12   |      |      |

1. SMPS output voltage 1.2 V, LDOs disable.

## 4.5 General characterization

### Table 12. General characteristics

| Parameter           |          | Тур.       | Unit |

|---------------------|----------|------------|------|

| Frequency range     |          | 430 - 470  | MHz  |

|                     |          |            |      |

|                     |          |            |      |

| Data rate DR        | 2-(G)FSK | 0.1 - 250  | kbps |

|                     | 4-(G)FSK | 0.2 - 500  |      |

| OOK/ASK             |          | 0.1 -125   |      |

| Data rate accuracy  |          | ±100       | ppm  |

| Frequency deviation | n FDEV   | 0.15 - 500 | kHz  |

If "Manchester" or "3-out-of-6" or FEC coding options are enabled the actual bit rate is affected as follows:

### Table 13. Data rate with different coding options

| Coding option | 4(G)FSK data rate [kbps] |

|---------------|--------------------------|

| NRZ           | 500                      |

| FEC           | 250                      |

| Manchester    | 250                      |

| 3-out-of-6    | 333.3                    |

## 4.6 Frequency synthesizer

### Table 14. Frequency synthesizer parameters

| Devenuetor          | Test conditions            |        |      |

|---------------------|----------------------------|--------|------|

| Parameter           | Test conditions            | 50 MHz | Unit |

| Frequency step size | Out-loop divider ratio = 4 | 23.8   | Hz   |

| 4 | 2 |  |

|---|---|--|

|   |   |  |

| Parameter                             | Test conditions                              | 50 MHz | Unit   |  |

|---------------------------------------|----------------------------------------------|--------|--------|--|

|                                       |                                              |        |        |  |

| RF carrier phase noise 433 MHz        | 10 kHz                                       | -109   | dBc/Hz |  |

|                                       | 100 kHz                                      | -110   |        |  |

|                                       | 1 MHz                                        | -124   |        |  |

|                                       | 10 MHz                                       | -141   |        |  |

| RF carrier phase noise 510 MHz        | 10 kHz                                       | -108   |        |  |

|                                       | 100 kHz                                      | -109   |        |  |

|                                       | 1 MHz                                        | -124   | -      |  |

|                                       | 10 MHz                                       | -140   | -      |  |

| RF carrier phase noise 868 MHz        | 10 kHz                                       | -102   |        |  |

|                                       | 100 kHz                                      | -103   |        |  |

|                                       | 1 MHz                                        | -117   | -      |  |

|                                       | 10 MHz                                       | -138   |        |  |

| RF carrier phase noise 915 MHz        | 10 kHz                                       | -102   |        |  |

|                                       | 100 kHz                                      | -102   | -      |  |

|                                       | 1 MHz                                        | -117   |        |  |

|                                       | 10 MHz                                       | -138   |        |  |

| PLL tuning voltage settling time @ 1% | Typical intermediate frequency (IF): 300 kHz | 75     | μs     |  |

| (Ready to LOCKON transition)          |                                              |        |        |  |

| PLL calibration time                  |                                              | 28     | μs     |  |

## 4.7 Crystal oscillator

Characteristics measured over recommended operating conditions unless otherwise specified. All typical values are referred to 25 °C temperature,  $V_{BAT}$  = 3.0 V.

The device supports crystals in the range [24-26] MHz and [48-52] MHz.

If the crystal is in the [24–26] MHz range, both the analog and the digital parts must work at this frequency. Otherwise, if a crystal in the [48-52] MHz range is used, the analog part must work at this frequency and the digital part at this frequency divided by 2. From now on in this document the XTAL oscillator will be indicated with  $f_{XO}$  and the digital clock with  $f_{dig}$

The divider for the digital part can be set by the PD\_CLKDIV bit of the XO\_RCO\_CONFIG1 in the following way:

• if a [48 – 52] MHz crystal is used, this bit must be 0 (digital divider enabled):

$$dig = \frac{f_{XO}}{2} \tag{1}$$

• if a [24 – 26] MHz crystal is used, this bit must be 1 (digital divider disabled):

$$f_{dig} = f_{\chi o} \tag{2}$$

The safest procedure to disable the divider without any risk of glitches in the digital clock is to switch into STANDBY mode, hence, disable the divider through register setting, and then come back to the READY state.

f

In order to avoid potential RF performance degradations, the crystal frequency should be chosen to satisfy the following equation:

$$nF_{CH} - \text{ROUND}\left(n\frac{F_{CH}}{f_{XO}}\right) f_{XO} \ge 1 \text{MHz}$$

(3)

where n is an integer in the set [1-7, B] (B is the synthesizer's divider ratio).

| Parameter                                                                   | Test conditions                          | Min. | Тур. | Max. | Unit   |

|-----------------------------------------------------------------------------|------------------------------------------|------|------|------|--------|

| Crystal frequency                                                           |                                          | 24   |      | 26   | MHz    |

|                                                                             |                                          | 48   |      | 52   |        |

| Frequency tolerance (1)                                                     |                                          |      | ± 40 |      | ppm    |

| Minimum requirement on external reference phase noise mask                  | 10 kHz                                   |      |      | -135 | dBc/Hz |

| $f_{XO} = 26 \text{ MHz}$ , to avoid degradation on synthesizer phase/noise | 100 kHz                                  |      |      | -140 |        |

|                                                                             | 1 MHz                                    |      |      | -140 |        |

|                                                                             | 10 MHz                                   |      |      | -140 |        |

| Programmable trans-conductance of the oscillator at start-up                |                                          | 13   |      | 43   | mS     |

| Start-up time (2)                                                           | VBAT=1.8 V,<br>$f_{XO} = 26 \text{ MHz}$ |      | 100  |      | μs     |

1. Including initial tolerance, crystal loading, aging, and temperature dependence. The acceptable crystal tolerance depends on RF frequency and channel spacing/bandwidth.

2. Start-up times are crystal dependent. The crystal oscillator trans-conductance can be tuned to compensate the variation of crystal oscillator series resistance.

### Table 16. Ultra-low power RC oscillator

| Parameter                            | Test conditions                                                                  | Тур.                | Unit |

|--------------------------------------|----------------------------------------------------------------------------------|---------------------|------|

| Calibrated frequency                 | Calibrated RC oscillator frequency is derived from crystal oscillator frequency. | 33.3 <sup>(1)</sup> | kHz  |

| Frequency accuracy after calibration |                                                                                  | ±1                  | %    |

1. Depending on the crystal frequency, the reported value is referring to 50 MHz.

### 4.8 RF receiver

Characteristics measured over recommended operating conditions unless otherwise specified. All typical values are referred to 25 °C temperature,  $V_{BAT}$  = 3.0 V, no frequency offset in the RX signal. The whole performance is referred to the STEVAL-FKI433V1, STEVAL-FKI512V1 or STEVAL-FKI868V1 with a 50 Ohm antenna connector.

### Table 17. RF receiver characteristics

| Parameter                         | Test conditions                                    |         | HPM/LPMSMPS<br>on typ. | Unit |

|-----------------------------------|----------------------------------------------------|---------|------------------------|------|

| Receiver channel bandwidth<br>CHF |                                                    |         | 1-800                  | kHz  |

| RX input return loss              | Max. RX gain, tied (RX + TX) matching networks     | 433 MHz | -15                    | dB   |

|                                   |                                                    |         | -15                    |      |

| Saturation 1% BER                 | BER 2-FSK 1.2 kHz FDEV, DR = 1.2 kbps, CHF = 4 kHz | 433 MHz | 10                     | dBm  |

|                                   |                                                    | 868 MHz | 10                     |      |

| Input third order intercept point |                                                    | 433 MHz | -25                    |      |

|                                   | offset from carrier                                | 868 MHz | -25                    |      |

| RX noise figure                   |                                                    | 433 MHz | 8                      | dB   |

|                                   |                                                    | 868 MHz | 8                      |      |

| Parameter                       | Test conditions |         | HPM/LPMSMPS<br>on typ. | Unit  |

|---------------------------------|-----------------|---------|------------------------|-------|

| Differential input impedance at | Max. RX gain    | 433 MHz | 200 // 1.5             | Ω//pF |

| LNA                             | R // C          | 868 MHz | 200 // 1.5             |       |

## 4.8.1 Blocking and selectivity at 433 MHz

| Parameter                                                                                     | Test condition               | HPM<br>SMPS on<br>(typ.) | LPM<br>SMPS ON<br>typ. | Unit |

|-----------------------------------------------------------------------------------------------|------------------------------|--------------------------|------------------------|------|

| Selectivity and blocking 1%<br>BER @ 2-GFSK BT=0.5 1.2 kHz FDEV, DR = 1.2 kbps, CHF = 4 kHz   | +12.5 kHz (adjacent channel) | 64                       | 56                     | dB   |

|                                                                                               | -12.5 kHz (adjacent channel) | 64                       | 56                     |      |

|                                                                                               | +25 kHz (alternate channel)  | 65                       | 59                     |      |

|                                                                                               | -25 kHz (alternate channel)  | 65                       | 59                     |      |

|                                                                                               | Image rejection              | 60                       | 63                     |      |

|                                                                                               | ±2 MHz                       | 81                       | 81                     |      |

|                                                                                               | ±10 MHz                      | 82                       | 85                     |      |

| Selectivity and blocking 1%<br>BER @ 2-GFSK BT=0.5 20 kHz FDEV, DR = 38.4 kbps, CHF = 100 kHz | +100 kHz (adjacent channel)  | 50                       | 37                     | dB   |

| g                                                                                             | -100 kHz (adjacent channel)  | 50                       | 37                     |      |

|                                                                                               | +200 kHz (alternate channel) | 51                       | 45                     |      |

|                                                                                               | -200 kHz (alternate channel) | 51                       | 45                     |      |

|                                                                                               | Image rejection              | 56                       | 58                     |      |

|                                                                                               | ±2 MHz                       | 67                       | 67                     |      |

|                                                                                               | ±10 MHz                      | 69                       | 72                     |      |

### Table 18. Blocking and selectivity at 433 MHz

## 4.8.2 Sensitivity at 433 MHz

### Table 19. Sensitivity at 433 MHz

| Parameter                | Test conditions                              | HPM/LPM SMPS on (typ.) | Unit |

|--------------------------|----------------------------------------------|------------------------|------|

| Sensitivity              | DR = 0.3 kbps, FDEV = 0.25 kHz, CHF = 1 kHz  | -128                   | dBm  |

| 1% BER @ 2-GFSK BT = 0.5 | DR = 1.2 kbps, FDEV = 1.2 kHz, CHF = 4 kHz   | -122                   |      |

|                          | DR = 38.4 kbps, FDEV = 20 kHz, CHF = 100 kHz | -109                   |      |

|                          | DR = 250 kbps, FDEV = 125 kHz, CHF = 780 kHz | -101                   |      |

| Sensitivity              | DR = 4.8 kbps, DEV = 2.4 kHz, CHF = 10 kHz   | -114                   | dBm  |

| 1% BER @ 4-GFSK BT = 0.5 | DR = 9.6 kbps, DEV = 4.8 kHz, CHF = 20 kHz   | -111                   |      |

|                          | DR = 19.2 kbps, DEV = 9.6 kHz, CHF = 40 kHz  | -108                   |      |

| Parameter    | Test conditions                 | HPM/LPM SMPS on (typ.) | Unit |

|--------------|---------------------------------|------------------------|------|

| Sensitivity  | DR = 0.3 kbps, CHF = 1 kHz -120 |                        | dBm  |

| 1% BER @ OOK | DR = 1.2 kbps, CHF = 4 kHz      | -118                   |      |

|              | DR = 38.4 kbps, CHF = 100 kHz   | -104                   |      |

|              | DR = 125 kbps, CHF = 250 kHz    | -100                   |      |

## 4.8.3 Blocking and selectivity @ 510 MHz

57

| Table 20. | <b>Blocking and</b> | selectivity | @ 510 MHz |

|-----------|---------------------|-------------|-----------|

|-----------|---------------------|-------------|-----------|

| Parameter                                                                                        | Test conditions              | HPM<br>SMPS on<br>(typ.) | LPM<br>SMPS on<br>(typ.) | Unit |

|--------------------------------------------------------------------------------------------------|------------------------------|--------------------------|--------------------------|------|

| Selectivity and blocking 1% BER @ 2-GFSK BT = 0.5, 1.2 kHz FDEV,<br>DR = 1.2 kbps, CHF = 4 kHz   | +12.5 kHz (adjacent channel) | 64                       | 56                       | dB   |

|                                                                                                  | -12.5 kHz (adjacent channel) | 65                       | 56                       |      |

|                                                                                                  | +25 kHz (alternate channel)  | 64                       | 59                       |      |

|                                                                                                  | -25 kHz (alternate channel)  | 65                       | 59                       |      |

|                                                                                                  | Image rejection              | 60                       | 63                       |      |

|                                                                                                  | ± 2 MHz                      | 81                       | 81                       |      |

|                                                                                                  | ± 10 MHz                     | 82                       | 85                       |      |

| Selectivity and blocking 1% BER @ 2-GFSK BT = 0.5, 20 kHz FDEV, DR<br>= 38.4 kbps, CHF = 100 kHz | +100 kHz (adjacent channel)  | 50                       | 37                       | dB   |

|                                                                                                  | -100 kHz (adjacent channel)  | 50                       | 37                       |      |

|                                                                                                  | +200 kHz (alternate channel) | 51                       | 45                       |      |

|                                                                                                  | -200 kHz (alternate channel) | 51                       | 45                       |      |

|                                                                                                  | Image rejection              | 56                       | 58                       |      |

|                                                                                                  | ± 2 MHz                      | 67                       | 67                       |      |

|                                                                                                  | ± 10 MHz                     | 69                       | 72                       |      |

## 4.8.4 Sensitivity at 510 MHz

### Table 21. Sensitivity at 510 MHz

| Parameter                | Test conditions                              | HPM/LPM SMPS on (typ.) | Unit |

|--------------------------|----------------------------------------------|------------------------|------|

| Sensitivity              | DR = 0.3 kbps, FDEV = 0.25 kHz, CHF = 1 kHz  | -128                   | dBm  |

| 1% BER @ 2-GFSK BT = 0.5 | DR = 1.2 kbps, FDEV = 1.2 kHz, CHF = 4 kHz   | -122                   |      |

|                          | DR = 38.4 kbps, FDEV = 20 kHz, CHF = 100 kHz | -109                   | -    |

|                          | DR = 250 kbps, FDEV = 125 kHz, CHF = 780 kHz | -101                   |      |

| Parameter                | Test conditions                             | HPM/LPM SMPS on (typ.) | Unit |

|--------------------------|---------------------------------------------|------------------------|------|

| Sensitivity              | DR = 4.8 kbps, DEV = 2.4 kHz, CHF = 10 kHz  | -114                   | dBm  |

| 1% BER @ 4-GFSK BT = 0.5 | DR = 9.6 kbps, DEV = 4.8 kHz, CHF = 20 kHz  | -111                   |      |

|                          | DR = 19.2 kbps, DEV = 9.6 kHz, CHF = 40 kHz | -108                   |      |

| Sensitivity              | DR = 0.3 kbps, CHF = 1 kHz                  | -120                   | dBm  |

| 1% BER @ OOK             | DR = 1.2 kbps, CHF = 4 kHz                  | -118                   |      |

|                          | DR = 38.4 kbps, CHF = 100 kHz               | -104                   |      |

|                          | DR = 125 kbps, CHF = 250 kHz                | -100                   |      |

## 4.8.5 Blocking and selectivity at 868 MHz

## Table 22. Blocking and selectivity @ 868 MHz

| Parameter                                                                                        | Test conditions              | HPM<br>SMPS on<br>(typ.) | LPM<br>SMPS on<br>(typ.) | Unit |

|--------------------------------------------------------------------------------------------------|------------------------------|--------------------------|--------------------------|------|

| Selectivity and blocking 1% BER @ 2-GFSK BT = 0.5, 1.2 kHz FDEV,<br>DR = 1.2 kbps, CHF = 4 kHz   | +12.5 kHz (adjacent channel) | 58                       | 50                       | dB   |

|                                                                                                  | -12.5 kHz (adjacent channel) | 58                       | 50                       |      |

|                                                                                                  | +25 kHz (alternate channel)  | 59                       | 51                       |      |

|                                                                                                  | -25 kHz (alternate channel)  | 59                       | 51                       | -    |

|                                                                                                  | Image rejection              | 58                       | 60                       |      |

|                                                                                                  | ± 2 MHz                      | 81                       | 81                       |      |

|                                                                                                  | ± 10 MHz                     | 82                       | 86                       |      |

| Selectivity and blocking 1% BER @ 2-GFSK BT = 0.5, 20 kHz FDEV, DR<br>= 38.4 kbps, CHF = 100 kHz | +100 kHz (adjacent channel)  | 44                       | 33                       | dB   |

|                                                                                                  | -100 kHz (adjacent channel)  | 44                       | 33                       |      |

|                                                                                                  | +200 kHz (alternate channel) | 45                       | 39                       |      |

|                                                                                                  | -200 kHz (alternate channel) | 45                       | 39                       |      |

|                                                                                                  | Image rejection              | 50                       | 55                       |      |

|                                                                                                  | ± 2 MHz                      | 67                       | 70                       |      |

|                                                                                                  | ± 10 MHz                     | 69                       | 73                       |      |

## 4.8.6 Sensitivity at 868 MHz

### Table 23. Sensitivity at 868 MHz

| Parameter                | Test conditions                              | HPM/LPM/SMPS on typ. | Unit |

|--------------------------|----------------------------------------------|----------------------|------|

| Sensitivity              | DR = 0.3 kbps, FDEV = 0.25 kHz, CHF = 1 kHz  | -128                 | dBm  |

| 1% BER @ 2-GFSK BT = 0.5 | DR = 1.2 kbps, FDEV = 1.2 kHz, CHF = 4 kHz   | -122                 | -    |

|                          | DR = 38.4 kbps, FDEV = 20 kHz, CHF = 100 kHz | -109                 |      |

|                          | DR = 250 kbps, FDEV = 125 kHz, CHF = 780 kHz | -101                 |      |

| Sensitivity              | DR = 4.8 kbps, DEV = 2.4 kHz, CHF = 10 kHz   | -114                 | dBm  |

| 1% BER @ 4-GFSK BT = 0.5 | DR = 9.6 kbps, DEV = 4.8 kHz, CHF = 20 kHz   | -111                 |      |

|                          | DR = 19.2 kbps, DEV = 9.6 kHz, CHF = 40 kHz  | -108                 |      |

| Sensitivity              | DR = 0.3 kbps, CHF = 1 kHz                   | -120                 | dBm  |

| 1% BER @ OOK             | DR = 1.2 kbps, CHF = 4 kHz                   | -118                 |      |

|                          | DR = 38.4 kbps, CHF = 100 kHz                | -104                 |      |

|                          | DR = 125 kbps, CHF = 250 kHz                 | -100                 |      |

## 4.8.7 Blocking and selectivity at 915 MHz

### Table 24. Blocking and selectivity at 915 MHz

| Parameter                                                                                     | Test condition               | HPM/<br>SMPS on<br>typ. | LPM/<br>SMPS on<br>typ. | Unit |

|-----------------------------------------------------------------------------------------------|------------------------------|-------------------------|-------------------------|------|

| Selectivity and blocking 1%<br>BER @ 2-GFSK BT=0.5 1.2 kHz FDEV, DR = 1.2 kbps, CHF = 4 kHz   | +12.5 kHz (adjacent channel) | 58                      | 50                      | dB   |

|                                                                                               | -12.5 kHz (adjacent channel) | 58                      | 50                      |      |

|                                                                                               | +25 kHz (alternate channel)  | 59                      | 51                      |      |

|                                                                                               | -25 kHz (alternate channel)  | 59                      | 51                      |      |

|                                                                                               | Image rejection              | 58                      | 60                      |      |

|                                                                                               | ±2 MHz                       | 81                      | 81                      |      |

|                                                                                               | ±10 MHz                      | 82                      | 86                      |      |

| Selectivity and blocking 1%<br>BER @ 2-GFSK BT=0.5 20 kHz FDEV, DR = 38.4 kbps, CHF = 100 kHz | +100 kHz (adjacent channel)  | 44                      | 33                      | dB   |

|                                                                                               | -100 kHz (adjacent channel)  | 44                      | 33                      |      |

|                                                                                               | +200 kHz (alternate channel) | 45                      | 39                      |      |

|                                                                                               | -200 kHz (alternate channel) | 45                      | 39                      |      |

|                                                                                               | Image rejection              | 50                      | 55                      |      |

|                                                                                               | ±2 MHz                       | 67                      | 70                      |      |

|                                                                                               | ±10 MHz                      | 69                      | 73                      |      |

## 4.8.8 Sensitivity at 915 MHz

### Table 25. Sensitivity at 915 MHz

| Parameter                | Test conditions                              | HPM/LPM/SMPS on typ. | Unit |

|--------------------------|----------------------------------------------|----------------------|------|

| Sensitivity              | DR = 0.3 kbps, FDEV = 0.25 kHz, CHF = 1 kHz  | -128                 | dBm  |

| 1% BER @ 2-GFSK BT = 0.5 | DR = 1.2 kbps, FDEV = 1.2 kHz, CHF = 4 kHz   | -122                 | -    |

|                          | DR = 38.4 kbps, FDEV = 20 kHz, CHF = 100 kHz | -109                 |      |

|                          | DR = 250 kbps, FDEV = 125 kHz, CHF = 780 kHz | -101                 |      |

| Sensitivity              | DR = 4.8 kbps, DEV = 2.4 kHz, CHF = 10 kHz   | -114                 | dBm  |

| 1% BER @ 4-GFSK BT = 0.5 | DR = 9.6 kbps, DEV = 4.8 kHz, CHF = 20 kHz   | -111                 |      |

|                          | DR = 19.2 kbps, DEV = 9.6 kHz, CHF = 40 kHz  | -108                 |      |

| Sensitivity              | DR = 0.3 kbps, CHF = 1 kHz                   | -120                 | dBm  |

| 1% BER @ OOK             | DR = 1.2 kbps, CHF = 4 kHz                   | -118                 |      |

|                          | DR = 38.4 kbps, CHF = 100 kHz                | -104                 |      |

|                          | DR = 125 kbps, CHF = 250 kHz                 | -100                 |      |

## 4.9 **RF transmitter**

Characteristics measured over recommended operating conditions unless otherwise specified. All typical values are referred to 25 °C temperature,  $V_{BAT}$  = 3.0 V. All performance is referred to the STEVAL-FKI433V1 or STEVAL-FKI868V1 with a 50  $\Omega$  antenna connector.

### Table 26. RF transmitter characteristics

| Parameter                          | Test conditions    | HPM typ. | LPM typ. | Unit |

|------------------------------------|--------------------|----------|----------|------|

| Maximum output power               | CW @ antenna level | 14       | 10       | dBm  |

| Maximum output power in boost mode | CW @ antenna level | 16       | 12       |      |

| Minimum output power               | CW @ antenna level | -30      | -30      |      |

| Output power step                  |                    | 0.5      | 0.5      | dB   |

### Table 27. PA impedance

| Parameter                          | Test conditions | Тур.   | Unit |

|------------------------------------|-----------------|--------|------|

| Optimum load impedance             | 433 MHz         | 56+25j | Ω    |

|                                    | 510 MHz         | 24+14j |      |

|                                    | 868 MHz         | 30+24j |      |

|                                    | 920 MHz         | 29+23j |      |

| Max permitted VSWR @ antenna level | 433 MHz         | 2      |      |

|                                    | 510 MHz         | 2      |      |

|                                    | 868 MHz         | 5      |      |

|                                    | 920 MHz         | 5      |      |

### Table 28. Regulatory standards

| Frequency band | Suitable for compliance with: |  |

|----------------|-------------------------------|--|

| 430 - 470 MHz  | ETSI EN300 220 category 1.5   |  |

| 470 - 512 MHz  | FCC part 15, FCC part 90      |  |

|                | ARIB STD-T67                  |  |

|                | Chinese SRRC                  |  |

| 860 - 940 MHz  | ETSI EN300 220-2 category 1.5 |  |

|                | FCC part 15                   |  |

|                | ARIB STD-T108                 |  |

|                | Chinese SRRC                  |  |

## 4.9.1 Harmonic emission at 433 MHz

### Table 29. Harmonic emission at 433 MHz

| Parameter | Test conditions | SMPS on | Unit |

|-----------|-----------------|---------|------|

| H1        | CW              | 14      | dBm  |

| H2        | CW              | -51     |      |

| H3        | CW              | -56     |      |

| H4        | CW              | -39     |      |

| H5        | CW              | -34     |      |

| H6        | CW              | -46     |      |

| H7        | CW              | -44     |      |

## 4.9.2 Harmonic emission at 510 MHz

### Table 30. Harmonic emission at 510 MHz

| Parameter | Test conditions | HPM/LPM/SMPS on | Unit |

|-----------|-----------------|-----------------|------|

| H1        | CW              | 14              | dBm  |

| H2        | CW              | -38             |      |

| H3        | CW              | -34             |      |

| H4        | CW              | -44             |      |

| H5        | CW              | -36             |      |

| H6        | CW              | -44             |      |

| H7        | CW              | -55             |      |

### 4.9.3 Harmonic emission at 868 MHz

### Table 31. Harmonic emission at 868 MHz

| Parameter | Test conditions | HPM/LPM/SMPS on | Unit |

|-----------|-----------------|-----------------|------|

| H1        | CW              | 14              | dBm  |

| H2        | CW              | -38             |      |

| H3        | CW              | -54             |      |

| H4        | CW              | -52             |      |

| H5        | CW              | -52             |      |

| H6        | CW              | -43             |      |

| H7        | CW              | -51             |      |

### 4.9.4 Harmonic emission at 915 MHz

### Table 32. Harmonic emission at 915 MHz

| Parameter | Test conditions | HPM/LPM/SMPS on | Unit |

|-----------|-----------------|-----------------|------|

| H1        | CW              | 14              | dBm  |

| H2        | CW              | -46             |      |

| H3        | CW              | -55             |      |

| H4        | CW              | -46             |      |

| H5        | CW              | -49             |      |

| H6        | CW              | -48             |      |

| H7        | CW              | -51             |      |

## 4.10 Digital interface specification

### Table 33. Digital SPI input, output and GPIO specification

| Parameter                      | Test conditions                                                        | Min.          | Тур. | Max.          | Unit |

|--------------------------------|------------------------------------------------------------------------|---------------|------|---------------|------|

| SPI clock frequency            |                                                                        |               | 8    | 10            | MHz  |

| Port I/O capacitance           |                                                                        |               | 1.4  |               | pF   |

| Rise time                      | From 0.1*VDD to 0.9*VDD, CL=20 pF (low output current programming)     |               | 6.0  |               | ns   |

|                                | From 0.1*VDD to 0.9*VDD, CL=20 pF (high<br>output current programming) |               | 2.5  |               |      |

| Fall time                      | From 0.1*VDD to 0.9*VDD, CL=20 pF (low<br>output current programming)  |               | 7.0  |               | ns   |

|                                | From 0.1*VDD to 0.9*VDD, CL=20 pF (high output current programming)    |               | 2.5  |               |      |

| Logic high level input voltage |                                                                        | VDD/2<br>+0.3 |      |               | V    |

| Logic low level input voltage  |                                                                        |               |      | VDD/8<br>+0.3 | V    |

| Parameter                                                | Test conditions                                        | Min.   | Тур. | Max. | Unit |

|----------------------------------------------------------|--------------------------------------------------------|--------|------|------|------|

| High level output voltage                                | IOH = -2.4 mA (-4.2 mA into high output current        | (5/8)* |      |      | V    |

|                                                          | mode).                                                 | VDD+   |      |      |      |

|                                                          |                                                        | 0.1    |      |      |      |

| Low level output voltage                                 | IOL = +2.0 mA (+4.0 mA into high output current mode). |        |      | 0.5  | V    |

| CSn low to positive edge on SCLK in low power mode state |                                                        |        | 40   |      | μs   |

| CSn low to positive edge on SCLK in ready state          |                                                        | 30     |      |      | ns   |

## 4.11 Battery indicator

Characteristics measured over recommended operating conditions unless otherwise specified. All typical values are referred to 25 °C temperature,  $V_{BAT}$  = 3.0 V.

| Parameter                     | Test conditions                                                          | Min. | Тур. | Max. | Unit |

|-------------------------------|--------------------------------------------------------------------------|------|------|------|------|

| Battery level thresholds #1   |                                                                          |      | 2.1  |      | V    |

| Battery level thresholds #2   |                                                                          |      | 2.3  |      |      |

| Battery level thresholds #3   |                                                                          |      | 2.5  |      |      |

| Battery level thresholds #4   |                                                                          |      | 2.7  |      |      |

| Brownout threshold            | Measured in slow battery variation (static) conditions (inaccurate mode) |      | 1.5  |      |      |

|                               | Measured in slow battery variation (static) conditions (accurate mode)   |      | 1.7  |      |      |

| Brownout threshold hysteresis |                                                                          |      | 70   |      | mV   |

### Table 34. Battery indicator and low battery detector

Note: For battery-powered equipment, the TX does not transmit at a wrong frequency under low battery voltage conditions. It remains on either channel or stops transmitting. The latter can of course be realized by using a lock detect and/or by switching off the PA under control of the battery monitor. For testing reasons this control is enabled/disabled by SPI.

## 5 Block description

### 5.1 Power management

The S2-LP integrates a high efficiency step-down converter cascaded with LDOs meant to supply both analog and digital parts. However, an LDO directly fed by the external battery provides a controlled voltage to the data interface block.

S2-LP's power management (PM) strategy, besides the basic functionality of providing different blocks with proper supplies, faces two main constraints: the first one is to implement such a power distribution with maximum efficiency, and the second one is to guarantee the isolation among critical blocks.

The efficiency target is obtained by using a switch mode power supply (SMPS) which converts the battery voltage (1.8 V - 3.6 V) to a lower voltage (settable from 1.2 V to 1.8 V) with efficiency higher than 90%.

The SMPS output voltage can be controlled by the SET\_SMPS\_LVL field in the PM\_CONF0 register. The relation between the SET\_SMPS\_LVL and the  $V_{OUT}$  of the SMPS is given by the following table:

| SET_SMPS_LVL | SMPS output voltage |

|--------------|---------------------|

| 001b         | 1.2 V               |

| 010b         | 1.3 V               |

| 011b         | 1.4 V               |

| 100b         | 1.5 V               |

| 101b         | 1.6 V               |

| 110b         | 1.7 V               |

| 111b         | 1.8 V               |

#### Table 35. SMPS output voltage

The SMPS output voltage can be controlled in TX only or for both RX and TX according to the SMPS\_LVL\_MODE bit of the PM\_CONF1 register.

- 1: SMPS output level will depend upon the value in PM\_CONFIG register just in TX state, while in RX state it will be fixed to 1.4 V.

- 0: SMPS output level will depend upon the value written in the PM\_CONFIG0 register (SET\_SMPS\_LEVEL field) both in RX and TX state.

The SMPS switching frequency is settable by the 2 registers PM\_CONF3 and PM\_CONF2.

If the KRM\_EN is 0, then the digital divider by 4 enabled. In this case SMPS' switching frequency is:

$$F_{SW} = \frac{f_{dig}}{4} \tag{1}$$

If the KRM\_EN is 1, the SMPS' switching frequency can be set by the KRM word according to the formula:

$$F_{SW} = K_{rm} \frac{f_{dig}}{2^{15}} \tag{2}$$

As  $f_{dig}$  is the digital domain frequency ( $f_{X0}$  if it is 24, 25 or 26 MHz) and ( $\frac{f_{X0}}{2}$  if  $f_{X0}$  is 48, 50 or 52 MHz).

All the RX measurements reported in this datasheet have been taken with a SMPS frequency set to 3 MHz (fdig = 25 MHz, PM\_CONF3 = 0x87, PM\_CONF2 = 0xFC). It is possible to have a little improvement of the sensitivity reducing the SMPS switching frequency but having as drawback a higher current consumption.

The isolation target is reached by using, for each critical block, a dedicated linear low-dropout regulator (LDO), which provides typically 1.2 V output voltage, either from battery level or from SMPS level, depending from the operating mode.

The S2-LP PM can be configured by SPI (BYPASS\_LDO field in PM\_CONFIG [1] register) in two main modes:

- 1. High performance mode (HPM)

- 2. Low power mode (LPM)

In HPM all available LDOs supplied from SMPS are used, to get the best possible isolation and minimum low-frequency noise level and SMPS ripple. SMPS must be set to 1.4 V at least.

In LPM the LDOs connected to the SMPS are by-passed and SMPS must be configured to provide 1.2 V output level to increase the regulation efficiency but with reduced isolation and higher low-frequency noise and SMPS ripple.

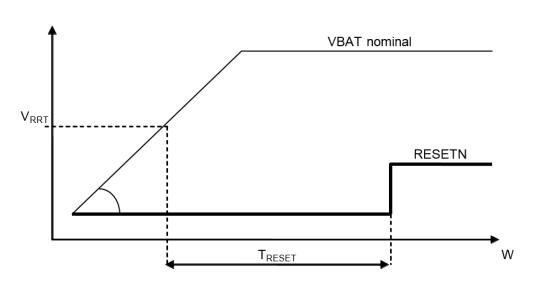

### 5.2 Power-On-Reset

The Power-On-Reset (POR) circuit generates a reset pulse upon power-up which is used to initialize the entire digital logic. Power-on-reset senses  $V_{BAT}$  voltage.

The S2-LP provides an automatic POR circuit, which generates an internal RESETN (active low) level for a time  $T_{RESET}$ , after the  $V_{BAT}$  reaches the reset release voltage threshold  $V_{RRT}$ , as shown in Figure 6. Power-On-Reset timing and limits. The same reset pulse is generated after a step-down on the input pin SDN (VDD>V<sub>RRT</sub>). This signal is available on the GPIO0 pin.

### Figure 6. Power-On-Reset timing and limits

The parameters VRRT and TRESET are fixed by design in order to guarantee a reliable reset procedure of the state machine. In addition, all the registers are initialized to their default values.

A software command SRES is also available, it generates an internal but partial resetting of the S2-LP.

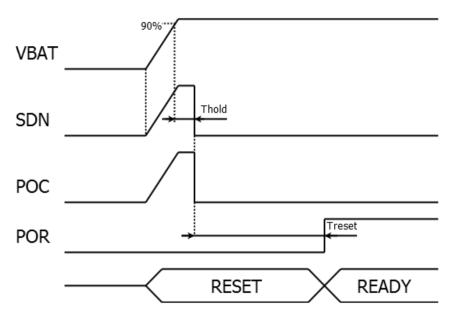

### Table 36. POR parameters

| Parameter                                             | Comment                 | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|-------------------------|------|------|------|------|

| Reset start-up threshold voltage                      |                         |      | 0.5  |      | V    |

| Hold pulse width (T <sub>hold</sub> , figure below)   | For SDN to be effective | 1    |      |      |      |

| Reset pulse width (T <sub>reset</sub> , figure below) |                         |      | 0.7  | 2    | ms   |

| Power-on VDD slope                                    |                         |      | 2.0  |      | V/ms |

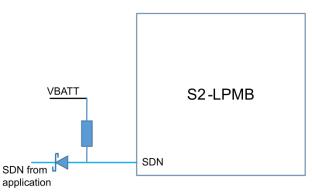

The following picture shows how the S2-LP must be controlled, i.e. the SDN signal must be tied to VBAT pin in order to avoid two potential issues during the start-up phase:

- 1. A cross conduction can appear on the GPIO until an available command is present on it.

- 2. The ESD protection diode from the SDN pad can sink current from the external driver connected to the SDN.

Also the SDN signal generates an internal signal (POC), which disables the digital I/Os when set to 1.

#### Figure 7. Start-up phase

Examples of possible connections

#### Figure 8. Examples of possible connections for SDN pin

### 5.3 RF synthesizer

A crystal connected to XIN and XOUT provides a clock signal to the frequency synthesizer. The allowed clock signal frequency is either 24, 25, 26, 48, 50, or 52 MHz.

As an alternative, an external clock signal feeds XIN for proper operation. In this option, XOUT can be left either floating or tied to ground.

Since the digital macro cannot be clocked at that double frequency (48, 50 or 52 MHz), a divided clock is used in this case (see Section 4.7 Crystal oscillator).

The integrated phase locked loop (PLL) is capable to synthesize a band of frequencies from 430 to 470 MHz, 470 to 512 MHz or from 860 to 940 MHz, providing the LO signal for the RX chain and the input signal for the PA in the TX chain.

Depending on the RF frequency and channel used, a very high accurate crystal or TCXO can be required.

The RF synthesizer implements fractional sigma delta architecture to allow fast settling and narrow channel spacing. It is fully integrated, and it uses a multi-band VCO to cover the whole frequency range. All internal calibrations are automatic.

According to the frequency synthesized the user must set the charge pump current according to the LO frequency variations, in order to have a constant loop bandwidth. The charge pump current is controlled by the PLL\_CP\_ISEL field (SYNT3 register) and the PLL\_PFD\_SPLIT\_EN (SYNTH\_CONFIG2). These fields should be set in the following way:

| VCO Freq (MHz) | fxo (MHz) | PLL_CP_ISEL | PLL_PFD_SPLIT_EN | ICP (µA) |

|----------------|-----------|-------------|------------------|----------|

| 3760           | 50        | 010         | 0                | 120      |

| 3760           | 25        | 001         | 1                | 200      |

| 3460           | 50        | 011         | 0                | 140      |

| 3460           | 25        | 010         | 1                | 240      |

### Table 37. Charge pump words

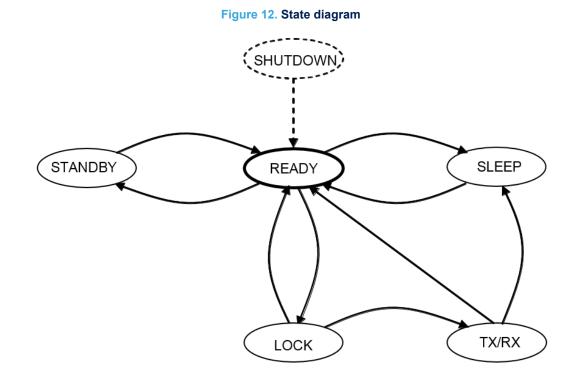

The S2-LP provides an automatic and very fast calibration procedure for the frequency synthesizer. If not disabled, it performs the calibration each time the synthesizer is required to lock to the programmed RF channel frequency (transaction from READY to LOCK/TX/RX or from RX to TX and vice versa). After completion, the S2-LP uses the calibration word and is stored in registers.

In order to get the synthesizer locked with the calibration procedure disabled, the correct calibration words must be previously stored in registers by user for TX and RX respectively. The advantage is reduce the LOCK setting time.

The transition time enables the S2-LP for frequency hopping operation due to its reduced response time and very quick programming synthesizer.

### 5.3.1 RF channel frequency settings

The channel center frequency can be programmed as follows:

### **Center frequency setting**

$$f_{c} = f_{base} + \left(\frac{f_{xo}}{2^{15}} \cdot CHSPACE\right) \cdot CHNUM$$

(1)

The  $f_{base}$  sets the main channel frequency; the value depends on the value of  $f_{x0}$  (the frequency of the XTAL oscillator, typically 24-26 MHz or 48-52 MHz.

### **Base frequency setting**

(3)

where:

57/

SYNT is a programmable 28-bits integer (SYNT[3:0] registers).

B is the out-of-loop SYNTH divider (BS field of the SYNT3 register):

PLL divider

$$B = \begin{cases} 4 \text{ for the high band} & (860 \text{ MHz to } 940 \text{ MHz, } BS = 0) \\ 8 \text{ for the middle band} & (430 \text{ MHz to } 512 \text{ MHz, } BS = 1) \end{cases}$$

D is the reference divider (REFDIV bit of XO\_RCO\_CONFIG0 register)

#### **Reference divider**

$$\boldsymbol{D} = \begin{cases} 1 \ if \ REFDIV = 0 \ (internal \ reference \ divider \ is \ disabled) \\ 2 \ if \ REFDIV = 1 \ (internal \ reference \ divider \ is \ enabled) \end{cases}$$

(4)

The resolution in the programmed value of the base frequency depends on the actual band selected.

#### Table 38. Resolution frequency

| fxo [MHz] | High band resolution [Hz] | Low band resolution [Hz] |

|-----------|---------------------------|--------------------------|

| 24        | 11.4                      | 5.7                      |

| 25        | 11.9                      | 6.0                      |

| 26        | 12.4                      | 6.2                      |

| 48        | 22.9                      | 11.4                     |

| 50        | 23.8                      | 11.9                     |

| 52        | 24.8                      | 12.4                     |

The f<sub>c</sub> is the frequency related to the channel specified. RF channels can be defined using the CHSPACE and CHNUM registers. In this way, it is possible to change faster the channel by changing just an 8-bits register, allowing the setting of 256 channels and frequency-hopping sequences. The actual channel spacing is from 793 Hz to 202342 Hz in 793 Hz steps for the 26 MHz configuration and from 1587 to 404685 Hz in 1587 Hz steps for the 52 MHz configuration.

#### Table 39. Channel spacing resolution

| fxo [MHz] | Channel spacing resolution [Hz] |

|-----------|---------------------------------|

| 24        | 732.42                          |

| 25        | 762.94                          |

| 26        | 793.45                          |

| 48        | 1464.84                         |

| 50        | 1525.88                         |

| 52        | 1586.91                         |

The S2-LP supports frequency modulation: 2-FSK, 4-FSK, 2-GFSK, 4-GFSK as well amplitude modulation OOK and ASK. Using register, the user can also program an unmodulated carrier for lab test and measurement. A special mode, direct polar modulation, allows building specific modulation scheme controlling directly the amplitude and the frequency of the carrier synthesized. The register MOD TYPE is used to select one of the following modulation scheme.

#### Table 40. Modulation scheme

| MOD_TYPE | Modulation scheme      |

|----------|------------------------|

| 000b     | 2-FSK                  |

| 001b     | 4-FSK                  |

| 010b     | 2-GFSK                 |

| 011b     | 4-GFSK                 |

| 101b     | ASK/OOK                |

| 110b     | Direct polar (TX only) |

| 111b     | CW                     |

#### 5.4.1 **Frequency modulation**

For frequency modulation 2-(G)FSK and 4-(G)FSK the frequency deviation can be tuned in wide range that depends on  $f_{\chi \rho}$  (XTAL frequency) according the following formula:

### **Frequency deviation**

$$f_{dev} = \begin{cases} \frac{f_{XO}}{2^{19}} \cdot \frac{round(D \cdot FDEV_M \cdot B/8)}{D \cdot B} & if FDEV_E = 0\\ \frac{f_{XO}}{2^{19}} \cdot \frac{round(D \cdot (256 + FDEV_M) \cdot 2^{(FDEV_E - 1)} \cdot B/8)}{D \cdot B} & if FDEV_E > 0 \end{cases}$$

(1)

Where  $f_{\chi_0}$  is the XTAL oscillation frequency, D is the reference divider and B is the band selector.

The frequency deviation programmed corresponds to the deviation of the outer constellation symbols. The deviation of the inner symbols is 1/3 of such programmed values, as reported in the table below, where 4 options are available.

Furthermore, since the payload is normally arranged in bytes, the arrangement can change the mapping for both 2-(G)FSK and 4-(G)FSK modulations, by using the CONST MAP (register MOD1), in the following way:

### Table 41. Constellation mapping 2-(G)FSK

| Format   | Symbol | CONST_MAP coding |    |       |    |  |

|----------|--------|------------------|----|-------|----|--|

|          |        | 0                | 1  | 2     | 3  |  |

| 2-(G)FSK | 0      | -FDEV            | NA | +FDEV | NA |  |

|          | 1      | +FDEV            | NA | -FDEV | NA |  |

### Table 42. Constellation mapping 4-(G)FSK

| Format   | Symbol | CONST_MAP coding |         |         |         |  |

|----------|--------|------------------|---------|---------|---------|--|

|          |        | 0                | 1       | 2       | 3       |  |

| 4-(G)FSK | 01     | -FDEV/3          | -FDEV   | +FDEV/3 | +FDEV   |  |

|          | 00     | -FDEV            | -FDEV/3 | +FDEV   | +FDEV/3 |  |

|          | 10     | +FDEV/3          | +FDEV   | -FDEV/3 | -FDEV   |  |

|          | 11     | +FDEV            | +FDEV/3 | -FDEV   | -FDEV/3 |  |

Furthermore, in the 4-(G)FSK it is also possible to swap the symbols using the 4FSK\_SYM\_SWAP field (register PCKTCTRL3) as follows:

When 4FSK\_SYM\_SWAP = 0:

$$\begin{cases} S0 = < b7b6 > \\ S1 = < b5b4 > \\ S2 = < b3b2 > \\ S3 = < b1b0 > \\ \end{cases}$$

When 4FSK\_SYM\_SWAP = 1

$$\begin{cases} S0 = < b6b7 > \\ S1 = < b4b5 > \\ S2 = < b2b3 > \\ S3 = < b0b1 > \\ \end{cases}$$

#### 5.4.1.1 Gaussian shaping

In 2-GFSK or 4-GFSK mode, the Gaussian filter BT product can be set by using the register BT\_SEL to 1 or 0.5.

The Gaussian filtering is implemented by poly-phase filtering with eight taps per symbol time. In order to further smooth the filter shape and improve spectral shaping, the output of the filter can be linearly interpolated by setting the register MOD\_INTERP\_EN.

A mathematical interpolation factor is applied at each sample of the Gaussian filter output. This factor is 64 for data rates corresponding to DATA\_RATE\_E < 5, it is automatically scaled as  $\frac{64}{2DATA_RATE_E - 5}$  for 5 ≤

DATA\_RATE\_E < 11 and it is automatically disabled for DATA\_RATE\_E = 11.

*Note:* The actual interpolation factor achieved may be limited by the minimal frequency resolution of the frequency synthesizer.

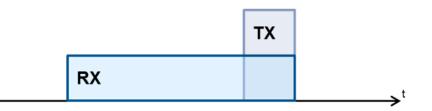

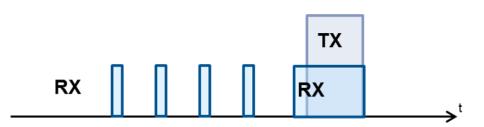

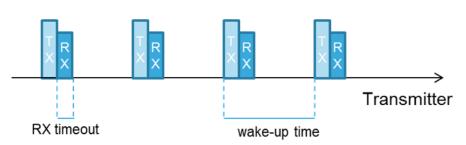

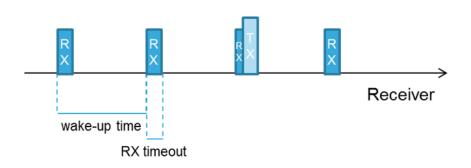

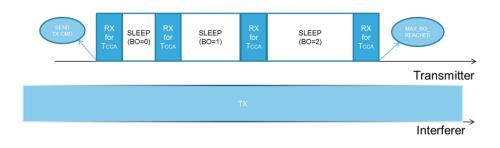

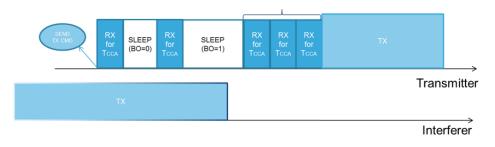

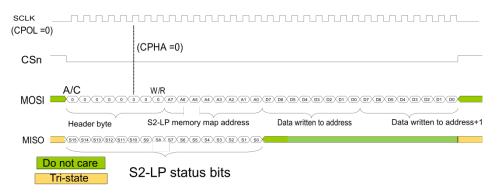

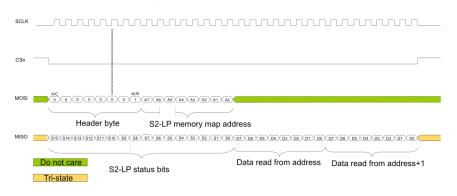

### 5.4.1.2 ISI cancellation 4-(G)FSK