- Главная

- О компании EBV

- Freescale

- Семейство недорогих 8-разрядным МК

- Семейство S12XA

- Семейство S12XE

- Семейство MC56F80xx

- Семейство MC56F800x

- Микроконтроллеры серии Flexis

- MCF51CN128 — самое экономичное 32-битное Ethernet решение

- Семейство MCF5222x

- Семейство MCF5223x

- Семейство MCF5225x

- Семейство MCF5227x

- Семейство MCF532x

- Семейство MCF5445x

- Семейство i.MX25

- Процессор i.MX27

- Процессор i.MX31

- Семейство i.MX35

- Процессор i.MX515

- Инструментальные средства для 8-битных м/к

- Инструментальные средства для 16/32-битных м/к

- Микросхемы управления питанием для процессорных систем

- MC34700: 9…18 Вольт, четырехканальный, многофункциональный импульсный источник питания

- MC34704: многоканальная интегральная схема управления питанием (PMIC)

- MC34726: 300 мА, высокоэффективный, с малым током покоя, синхронный понижающий стабилизатор с режимом Z-mode

- MC34727: 600 мА, высокоэффективный, с малым током покоя, синхронный понижающий стабилизатор с режимом Z-mode

- MC13783: микросхема управления питанием, аудио и пользовательскими интерфейсами с высоким уровнем интеграции

- Платформенные ИС для IEEE® 802.15.4/ZigBee приложений

- Датчики ускорения

- Датчики давления

Новое в мире полупроводников

Читаем, обсуждаем, задаем вопросы

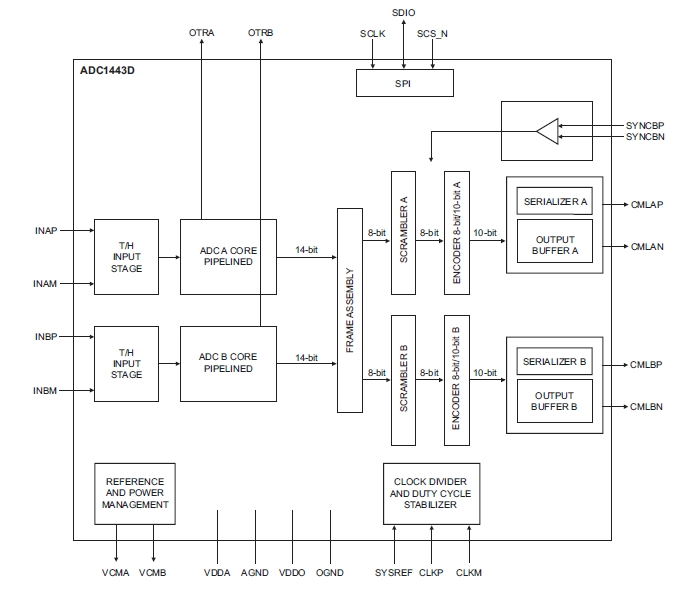

IDT: ADC1443D — 2-канальный 14-битный АЦП с частотой преобразования до 200 MSPS и малым энергопотреблением

Автор: admin23 Сен

Оптимизированный для применения в инфраструктуре систем беспроводной связи, новый аналого-цифровой преобразователь, отвечающий требованиям стандарта JEDEC JESD204B, обеспечивает превосходную линейность и минимальный уровень шумов на частоте преобразования до 200 MSPS (млн. выборок в сек.).

Оптимизированный для применения в инфраструктуре систем беспроводной связи, новый аналого-цифровой преобразователь, отвечающий требованиям стандарта JEDEC JESD204B, обеспечивает превосходную линейность и минимальный уровень шумов на частоте преобразования до 200 MSPS (млн. выборок в сек.).

Работающий от однополярного источника питания напряжением 1.8 В, ADC1443D200 оснащен последовательными выходами стандарта JESD204B, конфигурируемыми в один или два канала. Схема синхронизации нескольких устройств (MDS) позволяет с высокой точностью (сдвиг фазы не более 1 такта) синхронизировать до 16 каналов и 8 АЦП ADC1443D200. Интегрированный последовательный периферийный интерфейс SPI обеспечивает легкость конфигурирования и мониторинга работы АЦП. Программируемая схема входного каскада поддерживает полный размах входного напряжения от 1 ВПИК-ПИК до 2 ВПИК-ПИК.

Полоса частот входного аналогового сигнала до 1 ГГц (тип.) делает ADC1443D идеальным выбором для применения в мультистандартных, с несколькими несущими, коммуникационных приложениях. Выполненная по конвейерной архитектуре, схема коррекции ошибок на выходе гарантирует нулевые потери кода во всем заявленном рабочем диапазоне. ADC1443D200 доступен в 56-выводном корпусе HLQFN размером всего 8 х 8 мм и поддерживается различными демонстрационными комплектами. Также доступна 12-битная версия АЦП с быстродействием 125 MSPS, 160 MSPS или 200 MSPS.

|

| Внутренняя архитектура ADC1443D200 |

Отличительные особенности:

- 2-канальный АЦП с разрешением 14 бит

- Два последовательных выходных канала стандарта JESD204B с пропускной способностью 5 Гбит/с при напряжении питания 1.8 В

- Частота преобразования до 200 MSPS (млн. выборок в секунду)

- Мощность потребления 1 Вт, при частоте 200 MSPS

- Режим пониженного энергопотребления и режим сна

- Поддерживает работу в диапазоне температур от -40°C до +85°C

- Схема синхронизации нескольких устройств (MDS) позволяет объединить до 16 каналов до 8 АЦП

- Гарантированная совместимость с сериалайзерами/десериалайзерами (SerDes) ПЛИС FPGA производства Altera, Lattice и Xilinx

- Диапазон напряжения входного сигнала от 1 ВПИК-ПИК до 2 ВПИК-ПИК с шагом 1 дБ

- Делитель входной частоты от 1 до 8

- Стабилизатор рабочего цикла (DCS)

- Формат выходных данных: бинарное смещение, с дополнением до двух или код Грея

- Последовательный интерфейс SPI для управления настройками и мониторинга работы АЦП

- Соотношение сигнал/шум (SNR): 73 дБ (тип.), при частоте дискретизации FS = 185 MSPS, входной частоте FI = 190 МГц

- Свободный от искажений динамический диапазон (SFDR): 86 дБ (тип.), при частоте дискретизации FS = 185 MSPS, входной частоте FI = 190 МГц

- Интермодуляционные искажения третьего порядка (IMD3): 88 дБ (тип.), при частоте дискретизации FS = 185 MSPS, входной частоте FI1 = 188.5 МГц и FI2 = 191.5 МГц

- Полоса частот входного аналогового сигнала до 1 ГГц (тип.)

Область применения:

- Инфраструктура сетей беспроводной связи стандартов LTE, MC-GSM, WCDMA, TD-SCDMA

- Микроволновые ретрансляторы

- Программно-определяемые радиосистемы (Software Defined Radio — SDR)

- Аэрокосмические и военные системы связи

- Неинвазивные системы медицинской диагностики

- Промышленные анализаторы сигналов

- Научное оборудование

- Высокоскоростные приложения общего назначения

Запросить образцы, средства разработки или техническую поддержку

![]() Документация на ADC1443D (англ.)

Документация на ADC1443D (англ.)

Подпишись на новости! |

Рубрики

- Мероприятия

- Общие новости

- Технические новости

- Altera

- Analog Devices

- Amber

- AMS

- Aptina

- Atmel

- Avago

- Bridgelux

- Broadcom

- connectBlue

- Cypress

- Embit

- Everlight

- Fairchild

- Freescale

- Fujitsu

- IDT

- Infineon

- ISSI

- LS Power Semitech

- LS Research

- Luminus

- Lumotech

- Maxim Integrated

- Microchip

- Micron

- National Semiconductor

- Nexperia

- Numonyx

- NXP

- ON Semiconductor

- OSRAM

- Samsung

- Sensata

- SIMCom

- Spansion

- ST-Ericsson

- STMicroelectronics

- Texas Instruments

- Toshiba

- Vishay

- Vorago

- WEPTECH

- Xilinx

- Коммерческие новости

Метки

Архивы

- Август 2018

- Июнь 2018

- Май 2018

- Март 2018

- Февраль 2018

- Январь 2018

- Ноябрь 2017

- Октябрь 2017

- Сентябрь 2017

- Август 2017

- Июль 2017

- Июнь 2017

- Апрель 2017

- Март 2017

- Январь 2017

- Декабрь 2016

- Ноябрь 2016

- Октябрь 2016

- Сентябрь 2016

- Август 2016

- Июль 2016

- Июнь 2016

- Май 2016

- Апрель 2016

- Март 2016

- Февраль 2016

- Январь 2016

- Декабрь 2015

- Ноябрь 2015

- Октябрь 2015

- Сентябрь 2015

- Август 2015

- Июль 2015

- Июнь 2015

- Май 2015

- Апрель 2015

- Март 2015

- Февраль 2015

- Январь 2015

- Ноябрь 2014

- Октябрь 2014

- Сентябрь 2014

- Август 2014

- Июль 2014

- Июнь 2014

- Апрель 2014

- Март 2014

- Февраль 2014

- Декабрь 2013

- Ноябрь 2013

- Октябрь 2013

- Сентябрь 2013

- Август 2013

- Июль 2013

- Май 2013

- Апрель 2013

- Февраль 2013

- Январь 2013

- Декабрь 2012

- Ноябрь 2012

- Октябрь 2012

- Сентябрь 2012

- Август 2012

- Июль 2012

- Май 2012

- Апрель 2012

- Март 2012

- Февраль 2012

- Январь 2012

- Декабрь 2011

- Ноябрь 2011

- Октябрь 2011

- Сентябрь 2011

- Август 2011

- Июнь 2011

- Май 2011

- Апрель 2011

- Март 2011

- Февраль 2011

- Январь 2011

- Декабрь 2010

- Ноябрь 2010

- Октябрь 2010

- Сентябрь 2010

- Август 2010

- Июль 2010

- Июнь 2010

- Май 2010

- Апрель 2010

- Март 2010

- Февраль 2010

- Январь 2010

- Декабрь 2009

- Ноябрь 2009

- Октябрь 2009

- Сентябрь 2009

- Август 2009

- Июль 2009

- Июнь 2009

- Май 2009

- Апрель 2009

- Март 2009

- Февраль 2009

- Январь 2009

- Декабрь 2008

- Ноябрь 2008

- Октябрь 2008