- Главная

- О компании EBV

- Freescale

- Семейство недорогих 8-разрядным МК

- Семейство S12XA

- Семейство S12XE

- Семейство MC56F80xx

- Семейство MC56F800x

- Микроконтроллеры серии Flexis

- MCF51CN128 — самое экономичное 32-битное Ethernet решение

- Семейство MCF5222x

- Семейство MCF5223x

- Семейство MCF5225x

- Семейство MCF5227x

- Семейство MCF532x

- Семейство MCF5445x

- Семейство i.MX25

- Процессор i.MX27

- Процессор i.MX31

- Семейство i.MX35

- Процессор i.MX515

- Инструментальные средства для 8-битных м/к

- Инструментальные средства для 16/32-битных м/к

- Микросхемы управления питанием для процессорных систем

- MC34700: 9…18 Вольт, четырехканальный, многофункциональный импульсный источник питания

- MC34704: многоканальная интегральная схема управления питанием (PMIC)

- MC34726: 300 мА, высокоэффективный, с малым током покоя, синхронный понижающий стабилизатор с режимом Z-mode

- MC34727: 600 мА, высокоэффективный, с малым током покоя, синхронный понижающий стабилизатор с режимом Z-mode

- MC13783: микросхема управления питанием, аудио и пользовательскими интерфейсами с высоким уровнем интеграции

- Платформенные ИС для IEEE® 802.15.4/ZigBee приложений

- Датчики ускорения

- Датчики давления

Новое в мире полупроводников

Читаем, обсуждаем, задаем вопросы

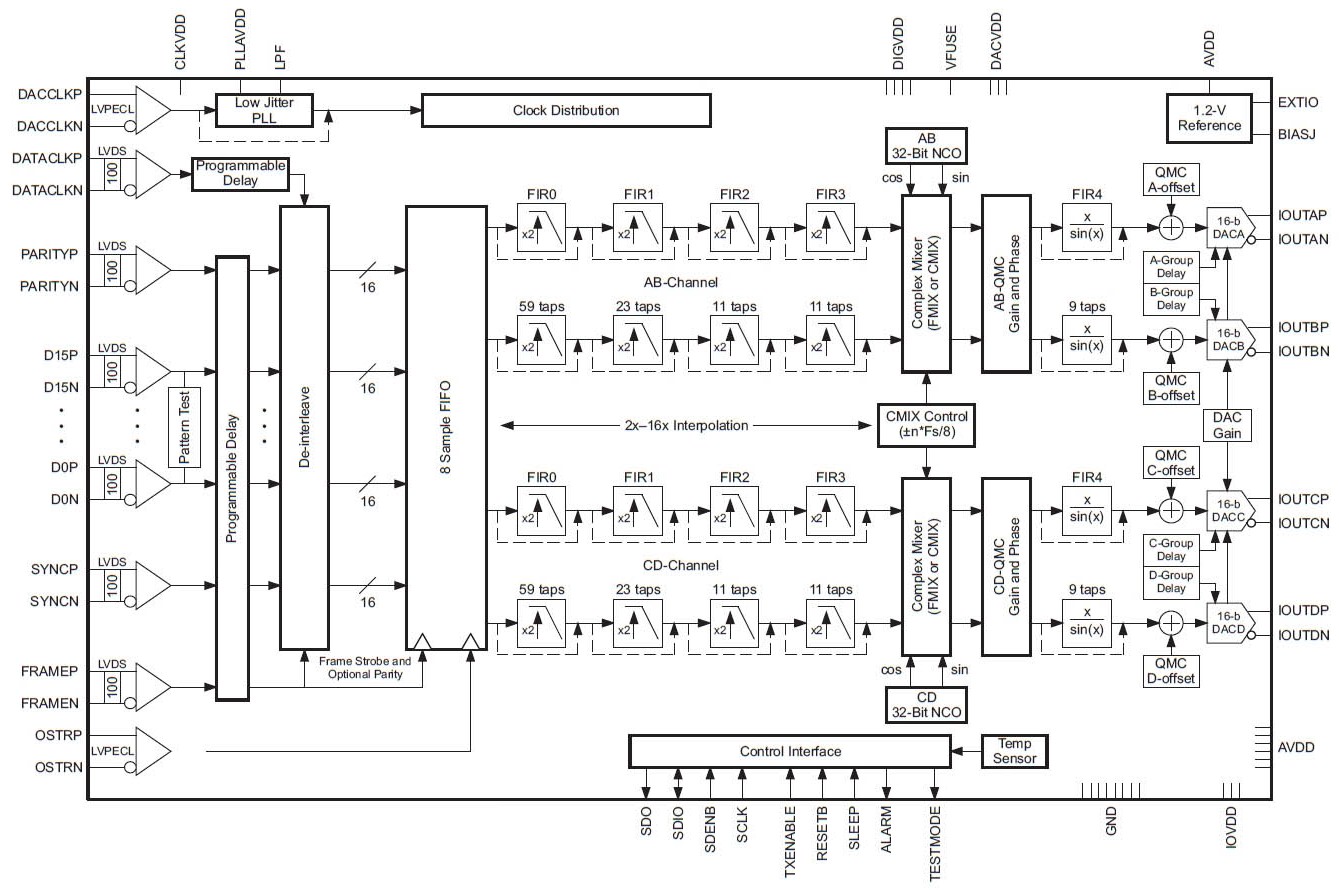

Texas Instruments: DAC3484 — 4-канальный Цифро-Аналоговый Преобразователь

Автор: admin29 Авг

Сверхнизкое энергопотребление, широкий динамический диапазон и частота преобразований до 1.25 GSPS (млрд. выборок в сек.)

Особенности устройства позволяют значительно упростить сложную архитектуру каналов передачи: интерполяционные фильтры 2-…16-го порядка с коэффициентом затухания в полосе задержки свыше 90 дБ упрощают схему интерфейса данных и восстанавливающих фильтров. Независимые комплексные смесители обеспечивают гибкую настройку несущей частоты.

Особенности устройства позволяют значительно упростить сложную архитектуру каналов передачи: интерполяционные фильтры 2-…16-го порядка с коэффициентом затухания в полосе задержки свыше 90 дБ упрощают схему интерфейса данных и восстанавливающих фильтров. Независимые комплексные смесители обеспечивают гибкую настройку несущей частоты.

Высокопроизводительный умножитель частоты с малым джиттером упрощает синхронизацию устройства без ощутимого снижения динамического диапазона. Цифровой блок коррекции квадратурного модулятора обеспечивает полную компенсацию коэффициента усиления, смещения, фазы и групповой задержки между каналами для промежуточной и несущей частот в приложениях с прямым преобразование с повышением частоты.

Цифровые данные поступают в устройство через 16-битныую LVDS шину с интегрированной схемой согласования. DAC3484 оснащен FIFO, схема проверки структуры данных и контроля по четности упрощает реализация входного интерфейса. Интерфейс также позволяет синхронизацию нескольких ЦАП.

|

| Внутренняя архитектура DAC3484 |

Отличительные особенности:

- Сверхнизкое энергопотребление: 1.2 Вт при 1.25 GSPS, полные рабочие характеристики

- Возможность синхронизации нескольких ЦАП

- Интерполяционный фильтр 2-, 4-, 8-, 16-го порядка

- Коэффициент затухания в полосе задержки свыше 90 дБ

- Гибкая схема смешения частот

- Два независимых высокоточных миксера с 32-битным NCO-генератором

- Энергосберегающие низко точные миксеры: ± n×Fs/8

- Высокопроизводительная система ФАПЧ умножения частоты с малым джиттером

- Цифровая схема коррекции для промежуточной и несущей частот:

- Коэффициента усиления, смещения, фазы и групповой задержки

- Цифровой инверсный Sinc-фильтр

- Гибкая 16-битная LVDS шина ввода данных

- 4-канальная 16-битная входная FIFO на 8 выборок

- Схема проверки структуры данных

- Контроль по четности

- GC5330-совместимая

- Датчик температуры

- Дифференциальный масштабируемый выход: от 10 мА до 30 мА

- Диапазон рабочих температур: -40…+85°C

- Компактный 88-выводной корпус mRQFN, размером 9 х 9 мм

|

Данная продукция сертифицирована по системе BAT (Best Accessible Technology). |

Запросить образцы, средства разработки или техническую поддержку

![]() Документация на DAC3484 (англ.)

Документация на DAC3484 (англ.)

![]() Руководство пользователя для демонстрационной платы DAC3484 EVM (англ.)

Руководство пользователя для демонстрационной платы DAC3484 EVM (англ.)

Подпишись на новости! |

Рубрики

- Мероприятия

- Общие новости

- Технические новости

- Altera

- Analog Devices

- Amber

- AMS

- Aptina

- Atmel

- Avago

- Bridgelux

- Broadcom

- connectBlue

- Cypress

- Embit

- Everlight

- Fairchild

- Freescale

- Fujitsu

- IDT

- Infineon

- ISSI

- LS Power Semitech

- LS Research

- Luminus

- Lumotech

- Maxim Integrated

- Microchip

- Micron

- National Semiconductor

- Nexperia

- Numonyx

- NXP

- ON Semiconductor

- OSRAM

- Samsung

- Sensata

- SIMCom

- Spansion

- ST-Ericsson

- STMicroelectronics

- Texas Instruments

- Toshiba

- Vishay

- Vorago

- WEPTECH

- Xilinx

- Коммерческие новости

Метки

Архивы

- Август 2018

- Июнь 2018

- Май 2018

- Март 2018

- Февраль 2018

- Январь 2018

- Ноябрь 2017

- Октябрь 2017

- Сентябрь 2017

- Август 2017

- Июль 2017

- Июнь 2017

- Апрель 2017

- Март 2017

- Январь 2017

- Декабрь 2016

- Ноябрь 2016

- Октябрь 2016

- Сентябрь 2016

- Август 2016

- Июль 2016

- Июнь 2016

- Май 2016

- Апрель 2016

- Март 2016

- Февраль 2016

- Январь 2016

- Декабрь 2015

- Ноябрь 2015

- Октябрь 2015

- Сентябрь 2015

- Август 2015

- Июль 2015

- Июнь 2015

- Май 2015

- Апрель 2015

- Март 2015

- Февраль 2015

- Январь 2015

- Ноябрь 2014

- Октябрь 2014

- Сентябрь 2014

- Август 2014

- Июль 2014

- Июнь 2014

- Апрель 2014

- Март 2014

- Февраль 2014

- Декабрь 2013

- Ноябрь 2013

- Октябрь 2013

- Сентябрь 2013

- Август 2013

- Июль 2013

- Май 2013

- Апрель 2013

- Февраль 2013

- Январь 2013

- Декабрь 2012

- Ноябрь 2012

- Октябрь 2012

- Сентябрь 2012

- Август 2012

- Июль 2012

- Май 2012

- Апрель 2012

- Март 2012

- Февраль 2012

- Январь 2012

- Декабрь 2011

- Ноябрь 2011

- Октябрь 2011

- Сентябрь 2011

- Август 2011

- Июнь 2011

- Май 2011

- Апрель 2011

- Март 2011

- Февраль 2011

- Январь 2011

- Декабрь 2010

- Ноябрь 2010

- Октябрь 2010

- Сентябрь 2010

- Август 2010

- Июль 2010

- Июнь 2010

- Май 2010

- Апрель 2010

- Март 2010

- Февраль 2010

- Январь 2010

- Декабрь 2009

- Ноябрь 2009

- Октябрь 2009

- Сентябрь 2009

- Август 2009

- Июль 2009

- Июнь 2009

- Май 2009

- Апрель 2009

- Март 2009

- Февраль 2009

- Январь 2009

- Декабрь 2008

- Ноябрь 2008

- Октябрь 2008