- Главная

- О компании EBV

- Freescale

- Семейство недорогих 8-разрядным МК

- Семейство S12XA

- Семейство S12XE

- Семейство MC56F80xx

- Семейство MC56F800x

- Микроконтроллеры серии Flexis

- MCF51CN128 — самое экономичное 32-битное Ethernet решение

- Семейство MCF5222x

- Семейство MCF5223x

- Семейство MCF5225x

- Семейство MCF5227x

- Семейство MCF532x

- Семейство MCF5445x

- Семейство i.MX25

- Процессор i.MX27

- Процессор i.MX31

- Семейство i.MX35

- Процессор i.MX515

- Инструментальные средства для 8-битных м/к

- Инструментальные средства для 16/32-битных м/к

- Микросхемы управления питанием для процессорных систем

- MC34700: 9…18 Вольт, четырехканальный, многофункциональный импульсный источник питания

- MC34704: многоканальная интегральная схема управления питанием (PMIC)

- MC34726: 300 мА, высокоэффективный, с малым током покоя, синхронный понижающий стабилизатор с режимом Z-mode

- MC34727: 600 мА, высокоэффективный, с малым током покоя, синхронный понижающий стабилизатор с режимом Z-mode

- MC13783: микросхема управления питанием, аудио и пользовательскими интерфейсами с высоким уровнем интеграции

- Платформенные ИС для IEEE® 802.15.4/ZigBee приложений

- Датчики ускорения

- Датчики давления

Новое в мире полупроводников

Читаем, обсуждаем, задаем вопросы

Freescale Semiconductor: MPC551x — 32-битный двухядерный микроконтроллер

Автор: admin21 Янв

Микроконтроллер, выполненный по двухядерной высокопроизводительной 32-битной архитектуре компании Freescale Semiconductor, для применения в автомобильной бортовой электронике и сетевых шлюзах

Микроконтроллер, выполненный по двухядерной высокопроизводительной 32-битной архитектуре компании Freescale Semiconductor, для применения в автомобильной бортовой электронике и сетевых шлюзах

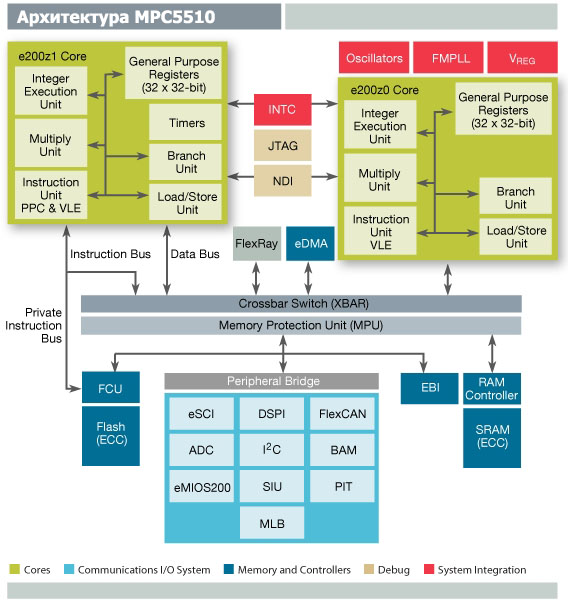

Семейство автомобильных контроллеров MPC5510 выполнено по технологии Power ArchitectureTM, которая подразумевает использование двух встроенных ядер e200z с рабочей частотой до 80МГц. Микроконтроллеры обладают высокой производительностью и гибкостью и, при этом, соответствуют требованиям к малому электропотреблению.

Семейство малопотребляющих микроконтроллеров MPC551x выполнено по технологии Power Architecture, которая согласована с постоянно усиливающимися вызовами улучшения рабочих характеристик и снижения себестоимости автомобильной бортовой электроники. Высокая скорость внутренней пересылки данных является результатом объединения двух ядер, блока eDMA и матричного коммутатора, который позволяет трем шинным мастерам одновременно осуществлять доступ к памяти и ресурсам ввода-вывода без участия ядра e200z1. Микроконтроллеры MPC551x могут использоваться для обработки данных, фильтрации в коммуникационных устройствах, эмуляции устройств ввода-вывода (например, дополнительных каналов ШИМ) или реализации интеллектуального сторожевого таймера, который реализует концепцию повышенной безопасности. Возможности оптимизации энергопотребления микроконтроллеров MPC551x представлены несколькими режимами остановки и сна, а также функциями конфигурации системы синхронизации. Данные возможности позволяют выполнить самые жесткие требования к статическому потреблению. В состав семейства входят микроконтроллеры с объемом встроенной Flash-памяти от 512 кБайт до 1.5 МБайт, одним или двумя ядрами, а также исполнения с поддержкой интерфейсов FlexRayTM и Media Local Bus для использования в сетевых шлюзах.

|

Отличительные особенности

- 32-битное ядро e200z1 совместимое с архитектурой Power ArchitectureTM, с поддержкой кода различной разрядности (Variable Length Encoding — VLE), обеспечивающей смешанное использование 16- и 32-битных комманд, для уменьшения размера кода прикладной программы

- Вторичное 16/32-битное ядро e200z0 только с поддержкой VLE

- До 1.5 МБайт FLASH памяти с кодом коррекции ошибок (ECC)

- Модуль FKASH памяти поддерживает функцию чтения во ввремя записи (RWW) и отличается малым размером сектора, обеспечивая поддержку различных начальных загрузчиков и эмуляцию функций EEPROM

- До 80 кБайт SRAM памяти с кодом коррекции ошибок (ECC)

- Модуль защиты памяти (MPU) с 16 регионами и 32-Байтной детализацией

- 16-канальный расширенный контроллер прямого доступа к памяти (eDMA)

- Модуль управления памятью (MMU) с буфером предыстории трансляций (TLB)

- Различные режима пониженного энергопотребления

- Поддержка отладочных интерфейсов JTAG и Nexus Class 2+

- Внутренний регулятор напряжения, преобразующий 5-вольтовое входное напряжение в 1.5- и 3.3-вольтовые уровни

- Диапазон рабочих температур: -40…+125°C

- Корпуса: 144-выводной LQFP и 208-выводной MAPBGA

Запросить образцы, средства разработки или техническую поддержку

![]() Документация на MPC5510 (англ.)

Документация на MPC5510 (англ.)

Подпишись на новости! |

Рубрики

- Мероприятия

- Общие новости

- Технические новости

- Altera

- Analog Devices

- Amber

- AMS

- Aptina

- Atmel

- Avago

- Bridgelux

- Broadcom

- connectBlue

- Cypress

- Embit

- Everlight

- Fairchild

- Freescale

- Fujitsu

- IDT

- Infineon

- ISSI

- LS Power Semitech

- LS Research

- Luminus

- Lumotech

- Maxim Integrated

- Microchip

- Micron

- National Semiconductor

- Nexperia

- Numonyx

- NXP

- ON Semiconductor

- OSRAM

- Samsung

- Sensata

- SIMCom

- Spansion

- ST-Ericsson

- STMicroelectronics

- Texas Instruments

- Toshiba

- Vishay

- Vorago

- WEPTECH

- Xilinx

- Коммерческие новости

Метки

Архивы

- Август 2018

- Июнь 2018

- Май 2018

- Март 2018

- Февраль 2018

- Январь 2018

- Ноябрь 2017

- Октябрь 2017

- Сентябрь 2017

- Август 2017

- Июль 2017

- Июнь 2017

- Апрель 2017

- Март 2017

- Январь 2017

- Декабрь 2016

- Ноябрь 2016

- Октябрь 2016

- Сентябрь 2016

- Август 2016

- Июль 2016

- Июнь 2016

- Май 2016

- Апрель 2016

- Март 2016

- Февраль 2016

- Январь 2016

- Декабрь 2015

- Ноябрь 2015

- Октябрь 2015

- Сентябрь 2015

- Август 2015

- Июль 2015

- Июнь 2015

- Май 2015

- Апрель 2015

- Март 2015

- Февраль 2015

- Январь 2015

- Ноябрь 2014

- Октябрь 2014

- Сентябрь 2014

- Август 2014

- Июль 2014

- Июнь 2014

- Апрель 2014

- Март 2014

- Февраль 2014

- Декабрь 2013

- Ноябрь 2013

- Октябрь 2013

- Сентябрь 2013

- Август 2013

- Июль 2013

- Май 2013

- Апрель 2013

- Февраль 2013

- Январь 2013

- Декабрь 2012

- Ноябрь 2012

- Октябрь 2012

- Сентябрь 2012

- Август 2012

- Июль 2012

- Май 2012

- Апрель 2012

- Март 2012

- Февраль 2012

- Январь 2012

- Декабрь 2011

- Ноябрь 2011

- Октябрь 2011

- Сентябрь 2011

- Август 2011

- Июнь 2011

- Май 2011

- Апрель 2011

- Март 2011

- Февраль 2011

- Январь 2011

- Декабрь 2010

- Ноябрь 2010

- Октябрь 2010

- Сентябрь 2010

- Август 2010

- Июль 2010

- Июнь 2010

- Май 2010

- Апрель 2010

- Март 2010

- Февраль 2010

- Январь 2010

- Декабрь 2009

- Ноябрь 2009

- Октябрь 2009

- Сентябрь 2009

- Август 2009

- Июль 2009

- Июнь 2009

- Май 2009

- Апрель 2009

- Март 2009

- Февраль 2009

- Январь 2009

- Декабрь 2008

- Ноябрь 2008

- Октябрь 2008