- Главная

- О компании EBV

- Freescale

- Семейство недорогих 8-разрядным МК

- Семейство S12XA

- Семейство S12XE

- Семейство MC56F80xx

- Семейство MC56F800x

- Микроконтроллеры серии Flexis

- MCF51CN128 — самое экономичное 32-битное Ethernet решение

- Семейство MCF5222x

- Семейство MCF5223x

- Семейство MCF5225x

- Семейство MCF5227x

- Семейство MCF532x

- Семейство MCF5445x

- Семейство i.MX25

- Процессор i.MX27

- Процессор i.MX31

- Семейство i.MX35

- Процессор i.MX515

- Инструментальные средства для 8-битных м/к

- Инструментальные средства для 16/32-битных м/к

- Микросхемы управления питанием для процессорных систем

- MC34700: 9…18 Вольт, четырехканальный, многофункциональный импульсный источник питания

- MC34704: многоканальная интегральная схема управления питанием (PMIC)

- MC34726: 300 мА, высокоэффективный, с малым током покоя, синхронный понижающий стабилизатор с режимом Z-mode

- MC34727: 600 мА, высокоэффективный, с малым током покоя, синхронный понижающий стабилизатор с режимом Z-mode

- MC13783: микросхема управления питанием, аудио и пользовательскими интерфейсами с высоким уровнем интеграции

- Платформенные ИС для IEEE® 802.15.4/ZigBee приложений

- Датчики ускорения

- Датчики давления

Новое в мире полупроводников

Читаем, обсуждаем, задаем вопросы

Texas Instruments: TMS320VC5505 — DSP-процессор с фиксированной точкой

Автор: admin24 Сен

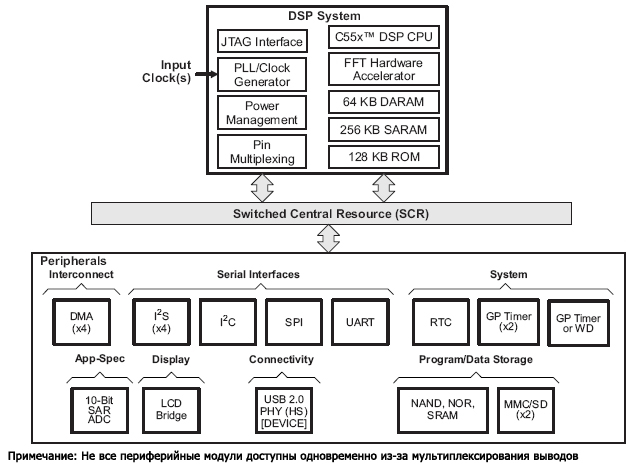

TMS320VC5505 – представитель DSP-процессоров с фиксированной точкой семейства TMS320C5000 от Texas Instruments для маломощных применений

TMS320VC5505 выполнен на основе ядра DSP-процессора TMS320C55. Высокая производительность и малое энергопотребление архитектуры C55 являются следствием повышения параллелизма и уделения серьезного внимания снижению потребляемой мощности. ЦПУ имеет собственную структуру шин, которая включает одну шину команд, одну 32-битную и две 16-битных шины чтения данных, две 16-битных шины записи данных и дополнительные шины для доступа к периферийным модулям и организации прямого доступа к памяти (DMA). Данные шины делают возможным выполнение за один цикл до четырех 16-битных операций чтения данных и двух 16-битных операций записи данных. TMS320VC5505 также содержит четыре DMA-контроллера. Каждый из них имеет 4 канала и, поэтому, всего имеется 16 независимых каналов передачи данных без вмешательства ЦПУ. При параллельной работе каждый из DMA-контроллеров может выполнить одну передачу данных за цикл, независимо от активности ЦПУ.

ЦПУ C55x имеет два блока MAC. Каждый из них может выполнить за один цикл умножение 17 бит x 17 бит вместе с 32-битным сложением. Основное 40-битное АЛУ дополнено еще одним 16-битным АЛУ. Выбор используемого АЛУ осуществляется инструкцией, что позволяет оптимизировать параллельно-выполняющиеся действия и потребляемую мощность. Управление перечисленными ресурсами осуществляется посредством блока адреса (AU) и блока данных (DU) ЦПУ C55x.

ЦПУ C55x имеет два блока MAC. Каждый из них может выполнить за один цикл умножение 17 бит x 17 бит вместе с 32-битным сложением. Основное 40-битное АЛУ дополнено еще одним 16-битным АЛУ. Выбор используемого АЛУ осуществляется инструкцией, что позволяет оптимизировать параллельно-выполняющиеся действия и потребляемую мощность. Управление перечисленными ресурсами осуществляется посредством блока адреса (AU) и блока данных (DU) ЦПУ C55x.

ЦПУ C55x использует набор инструкций с переменным числом байтов, что способствует улучшению плотности кода. Блок инструкций (IU) выполняет выборку 32-битных инструкций из внутренней или внешней памяти и создает очередь инструкций для блока программы (PU). Блок программы дешифрирует инструкции, формирует задания для блоков AU и DU, а также управляет полностью защищенным конвейером. Благодаря поддержке предсказаний переходов, исключена необходимость очистки конвейера при выполнении инструкций условного ветвления программы.

Возможности ввода/вывода общего назначения представлены 26 линиями (мультиплексированы с сигналами встроенных устройств) и 4 каналами 10-битного АЦП последовательного приближения. Для организации последовательной связи предусмотрено два интерфейса карт памяти MMC/SD, четыре модуля I2S, один модуль SPI с 4 выходами выбора микросхем, один модуль I2C с поддержкой режимов ведомый и мульти-мастер, а также интерфейс UART.

TMS320VC5505 оснащен интерфейсом внешней памяти (EMIF) для прямого подключения к микросхемам асинхронных запоминающих устройств (EPROM, NOR FLASH, NAND FLASH и SRAM). TMS320VC5505 также содержит контроллер USB 2.0 с режимом Устройство (Device) и часы реального времени (RTC). DMA-контроллер может выполнять передачу данных по 16 независимым каналам без участия ЦПУ, т.о. производительность передачи по каналам DMA может достигать двух 16-битных слов за цикл. DSP-процессор также содержит три таймера общего назначения (один из них может быть сконфигурирован для работы в качестве сторожевого таймера) и тактовый генератор на основе аналогового блока ФАПЧ (PLL).

Кроме того, TMS320VC5505 интегрирует аппаратный ускоритель быстрого преобразования Фурье (БПФ, FFT), напрямую подключенный к ЦПУ. Данный ускоритель поддерживает 8…1024-точечные (в степени 2) алгоритмы БПФ с действительными и комплексными числами.

|

Данная продукция сертифицирована по системе BAT (Best Accessible Technology). |

Запросить образцы, средства разработки или техническую поддержку

![]() Документация на TMS320VC5505 (англ.)

Документация на TMS320VC5505 (англ.)

Подпишись на новости! |

Рубрики

- Мероприятия

- Общие новости

- Технические новости

- Altera

- Analog Devices

- Amber

- AMS

- Aptina

- Atmel

- Avago

- Bridgelux

- Broadcom

- connectBlue

- Cypress

- Embit

- Everlight

- Fairchild

- Freescale

- Fujitsu

- IDT

- Infineon

- ISSI

- LS Power Semitech

- LS Research

- Luminus

- Lumotech

- Maxim Integrated

- Microchip

- Micron

- National Semiconductor

- Nexperia

- Numonyx

- NXP

- ON Semiconductor

- OSRAM

- Samsung

- Sensata

- SIMCom

- Spansion

- ST-Ericsson

- STMicroelectronics

- Texas Instruments

- Toshiba

- Vishay

- Vorago

- WEPTECH

- Xilinx

- Коммерческие новости

Метки

Архивы

- Август 2018

- Июнь 2018

- Май 2018

- Март 2018

- Февраль 2018

- Январь 2018

- Ноябрь 2017

- Октябрь 2017

- Сентябрь 2017

- Август 2017

- Июль 2017

- Июнь 2017

- Апрель 2017

- Март 2017

- Январь 2017

- Декабрь 2016

- Ноябрь 2016

- Октябрь 2016

- Сентябрь 2016

- Август 2016

- Июль 2016

- Июнь 2016

- Май 2016

- Апрель 2016

- Март 2016

- Февраль 2016

- Январь 2016

- Декабрь 2015

- Ноябрь 2015

- Октябрь 2015

- Сентябрь 2015

- Август 2015

- Июль 2015

- Июнь 2015

- Май 2015

- Апрель 2015

- Март 2015

- Февраль 2015

- Январь 2015

- Ноябрь 2014

- Октябрь 2014

- Сентябрь 2014

- Август 2014

- Июль 2014

- Июнь 2014

- Апрель 2014

- Март 2014

- Февраль 2014

- Декабрь 2013

- Ноябрь 2013

- Октябрь 2013

- Сентябрь 2013

- Август 2013

- Июль 2013

- Май 2013

- Апрель 2013

- Февраль 2013

- Январь 2013

- Декабрь 2012

- Ноябрь 2012

- Октябрь 2012

- Сентябрь 2012

- Август 2012

- Июль 2012

- Май 2012

- Апрель 2012

- Март 2012

- Февраль 2012

- Январь 2012

- Декабрь 2011

- Ноябрь 2011

- Октябрь 2011

- Сентябрь 2011

- Август 2011

- Июнь 2011

- Май 2011

- Апрель 2011

- Март 2011

- Февраль 2011

- Январь 2011

- Декабрь 2010

- Ноябрь 2010

- Октябрь 2010

- Сентябрь 2010

- Август 2010

- Июль 2010

- Июнь 2010

- Май 2010

- Апрель 2010

- Март 2010

- Февраль 2010

- Январь 2010

- Декабрь 2009

- Ноябрь 2009

- Октябрь 2009

- Сентябрь 2009

- Август 2009

- Июль 2009

- Июнь 2009

- Май 2009

- Апрель 2009

- Март 2009

- Февраль 2009

- Январь 2009

- Декабрь 2008

- Ноябрь 2008

- Октябрь 2008